Overview

| Information | |

|---|---|

| Data Bus Interface | PCI Bus 3.0 |

| # of Channels | 4 |

| Max Data Rate 5V (Mbps) | n/a |

| Max Data Rate 3.3V (Mbps) | 8 |

| Tx/Rx FIFO (Bytes) | n |

| FIFO Level Counters | |

| Program. Trigger Levels | |

| Auto Flow Control | |

| Auto RS-485 Half-Duplex Control | |

| Fractional Baud Rate Generator | |

| Power Down Mode | |

| 5V Tolerant Inputs | |

| Supply Voltage Range VCC (V) | |

| No. of GPIOs | |

| PCI Interface Supply Voltage Range VIO (V) | |

| Max UART/GPIO Input Voltage (V) | |

| Max UART/GPIO Output Voltage (V) | |

| Temperature Range (°C) | |

| Package |

The XR17V2541 (V254) is a single chip 4-channel 66MHz PCI (Peripheral Component Interconnect) UART (Universal Asynchronous Receiver and Transmitter) solution, optimized for higher performance and lower power. The V254 device with its fifth generation register set is designed to meet the high bandwidth and power management requirements for multi-serial communication ports for system administration and management. The 32-bit 66MHz PCI interface is compliant with PCI 3.0 and PCI power management revision 1.1 specifications. The device provides an upgrade path for MaxLinear’s 33MHz 5V and Universal PCI UART family of products in a 144-pin LQFP package.

The V254 consists of four independent UART channels, each with set of configuration and enhanced registers, 64 bytes of Transmit (TX) and Receive (RX) FIFOs, and a fractional Baud Rate Generator (BRG). A global interrupt source register provides a complete interrupt status indication for all 4 channels to speed up interrupt parsing. The V254 device operates at 33/66MHz and features fully programmable TX and RX FIFO level triggers, automatic hardware and software flow control, and automatic RS-485 half duplex direction control output for software and hardware design simplification.

1Covered by U.S. Patents #5,649,122 and #5,949,787

- High performance 32-bit 66MHz PCI UART

- PCI 3.0 compliance

- PCI power management rev. 1.1 compliance

- EEPROM interface for PCI configuration

- 3.3V supply with 5V tolerant non-PCI (serial) inputs

- Data read/write burst operation

- Global interrupt register for all four UART channels

- Up to 8 Mbps serial data rate

- Eight multi-purpose inputs/outputs

- A 16-bit general purpose timer/counter

- Sleep mode with wake-up Indicator

- Four independent UART channels controlled with

- 16C550 compatible register Set

- 64-byte TX and RX FIFOs with level counters and programmable trigger levels

- Fractional baud rate generator

- Automatic RTS/CTS or DTR/DSR hardware flow control with programmable hysteresis

- Automatic Xon/Xoff software flow control

- RS-485 half duplex direction control output with selectable turn-around delay

- Infrared (IrDA 1.0) data encoder/decoder

- Pb-Free, RoHS Compliant Versions Offered

- Remote Access Servers

- Storage Network Management

- Factory Automation and Process Control

- Instrumentation

- Multi-port RS-232/RS-422/RS-485 Cards

- Point-of-Sale Systems

Documentation & Design Tools

| Type | Title | Version | Date | File Size |

|---|---|---|---|---|

| Data Sheets | XR17V254 66 MHz PCI Bus Quad UART with Power Management Support | 1.0.1 | July 2008 | 1.3 MB |

| Application Notes | AN-225, Installing and Testing a PCI/PCIe UART Serial Port Using a Custom MaxLinear Driver in Linux | 1B | July 2018 | 427.1 KB |

| Application Notes | AN 209 - Windows & Linux API interface code for PCI/PCIe UARTs’ drivers | December 2011 | 199.5 KB | |

| Application Notes | AN-204, UART Sleep Mode | 1.0.0 | June 2010 | 515.8 KB |

| Application Notes | DAN-189, MaxLinear UARTs in GPS Applications | 1.0.0 | April 2008 | 139 KB |

| Application Notes | DAN-112, PCI UART - EEPROM Interface | June 2003 | 36.8 KB | |

| User Guides & Manuals | PCI/PCIe EEPROM Programming Utility User Manual | 1.0.0 | November 2010 | 262.5 KB |

| Software: GUIs & Utilities | PCI UART EEPROM Programming Utility | July 2017 | 10.9 KB | |

| Product Flyers | 66 MHz 32-bit PCI Bus Dual, Quad and Octal UARTs | 1.0.0 | August 2006 | 302.4 KB |

| Product Brochures | Interface Brochure | November 2023 | 3.7 MB | |

| Software: Drivers | Windows 10 | 5.5.0.0 | September 2020 | 319.1 KB |

| Software: Drivers | Linux 2.6.32 and newer | 2.6.0.0 | August 2019 | 20.2 KB |

| Software: Drivers | Windows XP, Vista, 7, 8, 8.1 | 5.3.0.0 | September 2015 | 275.2 KB |

| Software: Drivers | Linux 2.6.32 and newer | 2.0.0 | March 2015 | 15.4 KB |

| Software: Drivers | Linux 2.6.31 | 1.0.0 | June 2010 | 12.7 KB |

| Software: Drivers | Linux 2.4.x | 1.0.0 | December 2009 | 894.7 KB |

| Software: Drivers | Linux 2.6.16 | 1.0.0 | December 2009 | 12.8 KB |

| Software: Drivers | Linux 2.6.18 | 1.0.0 | December 2009 | 12.7 KB |

| Software: Drivers | Linux 2.6.21 | 1.0.0 | December 2009 | 12.8 KB |

| Software: Drivers | Linux 2.6.8 | 1.0.0 | December 2009 | 17.4 KB |

| Schematics & Design Files | PCI Eval Board Schematic | 1.1.0 | July 2007 | 126.3 KB |

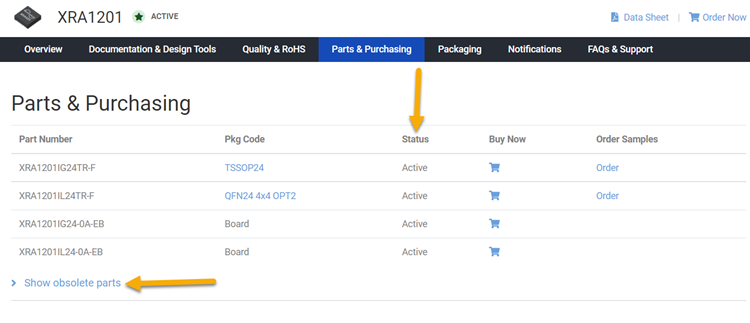

Parts & Purchasing

| Part Number | Pkg Code | Min Temp | Max Temp | Status | Suggested Replacement | PDN |

|---|---|---|---|---|---|---|

| XR17V254IV-F | LQFP144 | -40 | 85 | OBS | XR17V258IV-F | |

| XR17V254IV-F | LQFP144 | -40 | 85 | OBS | XR17D154IV-F | |

| XR17V254IVTR-F | LQFP144 | -40 | 85 | OBS | XR17D154IVTR-F | |

| XR17V254IVTR-F | LQFP144 | -40 | 85 | OBS | XR17V258IVTR-F |

Active - the part is released for sale, standard product.

EOL (End of Life) - the part is no longer being manufactured, there may or may not be inventory still in stock.

CF (Contact Factory) - the part is still active but customers should check with the factory for availability. Longer lead-times may apply.

PRE (Pre-introduction) - the part has not been introduced or the part number is an early version available for sample only.

OBS (Obsolete) - the part is no longer being manufactured and may not be ordered.

NRND (Not Recommended for New Designs) - the part is not recommended for new designs.

Packaging

Notifications

FAQs & Support

Search our list of FAQs for answers to common technical questions.

For material content, environmental, quality and reliability questions review the Quality tab or visit our Quality page.

For ordering information and general customer service visit our Contact Us page.

Submit a Technical Support Question As a New Question

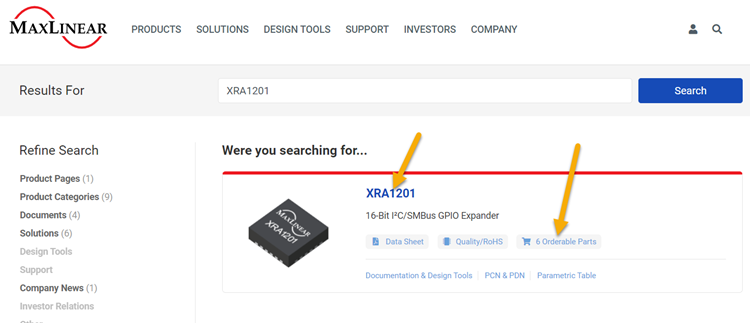

The Parts & Purchasing section of the product page shows the Status of all orderable part numbers for that product. Click Show obsolete parts, to see all EOL or OBS products.

1. Native drivers: Native drivers may be found in all major OS such as Windows, Linux, and Max OSX. Typically these drivers will be automatically loaded. In some cases, these are basic drivers and may have limitations on advanced device functionality, however. USB HID, Hub and CDC-ACM drivers are examples of native drivers. The CDC-ACM driver be used with our CDC-ACM class USB UARTs, but has limited functionality.

2. MaxLinear custom drivers: MaxLinear custom drivers may be used to support additional functionality in MaxLinear devices. For example, the MaxLinear custom driver for USB UARTs overcomes the limitations of the native CDC-ACM driver. See https://www.exar.com/design-tools/software-drivers for a list of and access to the drivers that we currently have. In some cases, the MaxLinear driver can also be customized, or source code can be provided after executing a Software License Agreement.

Please check that all the following conditions are satisfied first.

- no interrupts pending (ISR bit-0 = 1)

- modem inputs are not toggling (MSR bits 0-3 = 0)

- RX input pin is idling HIGH • divisor (the value in DLL register) is non-zero

- TX and RX FIFOs are empty

Be sure sleep mode bit has been set to 1. If there are multiple UART channels, the sleep conditions must be true for all channels.

See more on Sleep Mode in AN204 UART Sleep Mode.

Yes. Note: some devices do have powersave mode. If UART goes into powersave mode, then the registers are not accessible.

See more on Sleep Mode in AN204 UART Sleep Mode.

Read LSR register to check whether the UART receives the data or not.

- If LSR value is 0x60, it means that either UART receiver FIFO doesn’t receive the data or the data in receiver FIFO has been read out before the read of LSR.

- If LSR value is 0x00, it means data is still in the THR (clock doesn’t oscillate to transmit data).

- If LSR value is 0xFF, it means either UART is in powersave mode or UART is powered off. For those devices with powersave mode, be sure that UARTS are not in powersave mode.

See more on Sleep Mode in AN204 UART Sleep Mode.

- Check whether the register set can be accessed.

- Check whether the crystal is oscillating fully.

- Check whether the data can be transmitted in internal loopback mode.

See more on Sleep Mode in AN204 UART Sleep Mode.