MxL86110

**Ethernet PHY**

Single Port Gigabit Ethernet PHY

MxL86110C MxL86110I

# **Data Sheet**

Revision 1.1, 2023-02-20 Reference ID 620799

### Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

MaxLinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

\*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2023 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008

Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

| Current:  | Revision 1.1, 2023-02-20                                                                      |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Previous: | : Revision 1.0, 2022-11-30                                                                    |  |  |  |  |  |

| Page      | Major changes since previous revision                                                         |  |  |  |  |  |

| All       | Removed Preliminary statement from the document.                                              |  |  |  |  |  |

| 10        | Chapter 1, Product Overview: Updated chapter.                                                 |  |  |  |  |  |

| 14        | Chapter 2, External Signals: Updated chapter.                                                 |  |  |  |  |  |

| 24        | Chapter 3, Functional Description: Updated chapter.                                           |  |  |  |  |  |

| 33        | Chapter 4, MDIO and MMD Register Interface Description: Updated chapter.                      |  |  |  |  |  |

| 37        | Chapter 5.1, Standard Management Registers: Updated chapter.                                  |  |  |  |  |  |

| <b>59</b> | Chapter 5.2, PHY-specific Management Registers: Updated chapter.                              |  |  |  |  |  |

| 72        | Chapter 6.1, Standard PCS Registers for MMD=0003 <sub>H</sub> : Updated chapter.              |  |  |  |  |  |

| 75        | Chapter 6.2, Standard Auto-Negotiation Registers for MMD=0007 <sub>H</sub> : Updated chapter. |  |  |  |  |  |

| 79        | Chapter 7.1, Common Extended Register: Updated chapter.                                       |  |  |  |  |  |

| 105       | Chapter 7.2, UTP Extended Register: Updated chapter.                                          |  |  |  |  |  |

| 128       | Chapter 8, Electrical Characteristics: Updated chapter.                                       |  |  |  |  |  |

| 138       | Chapter 9, Package Outline: Updated chapter.                                                  |  |  |  |  |  |

| 144       | Terminology: Updated chapter.                                                                 |  |  |  |  |  |

### **Table of Contents**

## **Table of Contents**

|                    | Table of Contents                           | . 4 |

|--------------------|---------------------------------------------|-----|

|                    | List of Figures                             | . 7 |

|                    | List of Tables                              | . 8 |

|                    | Preface                                     | . 9 |

| 1                  | Product Overview                            | 10  |

| 1.1                | Features                                    | 11  |

| 1.2                | Block Diagram                               | 12  |

| 1.3                | Target Applications                         | 13  |

| 2                  | External Signals                            |     |

| 2.1                | Overview                                    |     |

| 2.2                | External Signal Description                 |     |

| 2.2.1              | Pin Diagram                                 |     |

| 2.2.2              | Abbreviations                               |     |

| 2.2.3              | Input/Output Signals                        |     |

| 2.2.3.1            | Ethernet Media Interface                    |     |

| 2.2.3.2<br>2.2.3.3 | RGMIILED Interface                          |     |

| 2.2.3.3<br>2.2.3.4 | Management Interfaces                       | _   |

| 2.2.3.4<br>2.2.3.5 | Miscellaneous Signals                       |     |

| 2.2.3.6            | Power Supply                                |     |

|                    | • • •                                       |     |

| 3                  | Functional Description                      |     |

| 3.1<br>3.2         | Management Interface                        |     |

| 3.2<br>3.3         | Auto-Negotiation (ANEG)                     |     |

| 3.4                | Loopback Mode                               |     |

| 3.4.1              | Near-End Test Loops                         |     |

| 3.4.2              | External Loopback                           |     |

| 3.4.3              | Far-End PHY Loopback                        |     |

| 3.5                | Energy Efficient Ethernet (EEE)             |     |

| 3.6                | Synchronous Ethernet (SyncE)                |     |

| 3.7                | Wake-On-LAN (WoL)                           |     |

| 3.8                | Link Down Power Saving (Sleep Mode)         |     |

| 3.9                | Interrupt                                   | 27  |

| 3.10               | Reset                                       | 28  |

| 3.11               | PHY Address                                 | 28  |

| 3.12               | RGMII Interface                             | 29  |

| 3.13               | LED Interface                               |     |

| 3.14               | MDINT Pin Usage                             |     |

| 3.15               | Power Supply Rails                          |     |

| 3.16               | Configuration by Pin Strapping              | 31  |

| 4                  | MDIO and MMD Register Interface Description |     |

| 4.1                | Definitions                                 |     |

| 4.2                | Register Naming and Numbering               |     |

| 4.2.1              | Register Numbering                          |     |

| 4.2.2              | Register Naming                             |     |

| 4.2.3              | Examples                                    | 34  |

### **Table of Contents**

| 1.3    | MMD Devices Present in MxL86110                                                    | . 35 |

|--------|------------------------------------------------------------------------------------|------|

| 1.4    | Responsibilities of the STA                                                        |      |

| 1.5    | MDIO Access Protocols to Read / Write Registers                                    | . 35 |

| 5      | MDIO Registers Detailed Description                                                | . 36 |

| 5.1    | Standard Management Registers                                                      | . 37 |

| 5.1.1  | Standard Management Registers                                                      | . 38 |

| 5.2    | PHY-specific Management Registers                                                  | . 59 |

| 5.2.1  | PHY Specific Function Control Register (Register 16)                               | . 60 |

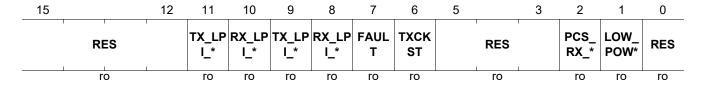

| 5.2.2  | PHY Specific Status Register (Register 17)                                         | . 61 |

| 5.2.3  | Interrupt Mask Register (Register 18)                                              | . 63 |

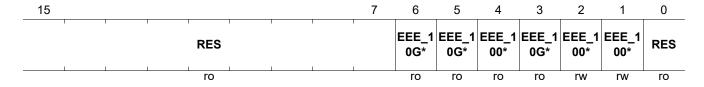

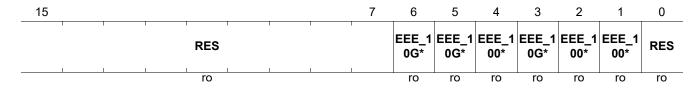

| 5.2.4  | Interrupt Status Register (Register 19)                                            | . 65 |

| 5.2.5  | Speed Auto Downgrade Control Register (Register 20)                                | . 67 |

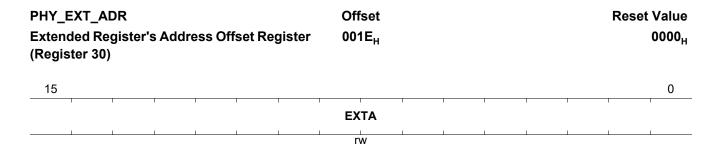

| 5.2.6  | Extended Register's Address Offset Register (Register 30)                          | . 69 |

| 5.2.7  | Extended Register's Data Register (Register 31)                                    | . 70 |

| :      | MMD Registers Detailed Description                                                 | 71   |

| 5.1    | Standard PCS Registers for MMD=0003 <sub>H</sub>                                   |      |

| 5.1.1  | Standard PCS Registers for MMD=0003 <sub>H</sub>                                   |      |

| 6.2    | Standard Auto-Negotiation Registers for MMD=0007 <sub>H</sub>                      |      |

| 5.2.1  | Standard Auto-Negotiation Registers for MMD=0007 <sub>H</sub>                      |      |

| J.Z. I |                                                                                    |      |

| 7      | Extended Register Detailed Description                                             |      |

| 7.1    | Common Extended Register                                                           |      |

| 7.1.1  | Chip Configuration Register (Register A001 <sub>H</sub> )                          |      |

| 7.1.2  | RGMII Configuration Register 1 (Register A003 <sub>H</sub> )                       |      |

| 7.1.3  | RGMII Configuration Register 2 (Register A004 <sub>H</sub> )                       |      |

| 7.1.4  | RGMII In-Band Status and MDIO Configuration Register (Register A005 <sub>H</sub> ) |      |

| 7.1.5  | Miscellaneous Control Register (Register A006 <sub>H</sub> )                       |      |

| 7.1.6  | Wake on LAN Address Byte 5 and 6 (Register A007 <sub>H</sub> )                     |      |

| 7.1.7  | Wake on LAN Address Byte 3 and 2 (Register A008 <sub>H</sub> )                     |      |

| 7.1.8  | Wake on LAN Address Byte 1 and 0 (Register A009 <sub>H</sub> )                     |      |

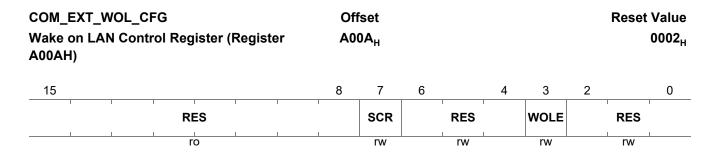

| 7.1.9  | Wake on LAN Control Register (Register A00A <sub>H</sub> )                         |      |

| 7.1.10 | LED General Configuration Register (Register A00B <sub>H</sub> )                   |      |

| 7.1.11 | LED0 Configuration Register (Register A00C <sub>H</sub> )                          |      |

| 7.1.12 | LED1 Configuration Register (Register A00D <sub>H</sub> )                          |      |

| 7.1.13 | LED2 Configuration Register (Register A00E <sub>H</sub> )                          |      |

| 7.1.14 | LED Blinking Configuration Register (Register A00F <sub>H</sub> )                  |      |

| 7.1.15 | Pin Driving Strength Configuration Register (Register A010 <sub>H</sub> )          |      |

| 7.1.16 | Pin Driving Strength Configuration Register (Register A012 <sub>H</sub> )          |      |

| 7.2    | UTP Extended Register                                                              |      |

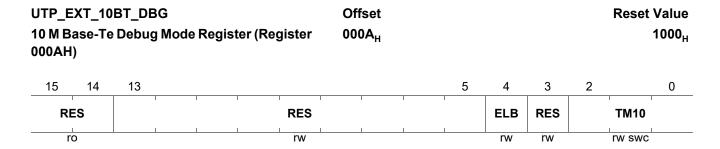

| 7.2.1  | 10 M Base-Te Debug Mode Register (Register 000A <sub>H</sub> )                     |      |

| 7.2.2  | Sleep Mode Control Register (Register 0027 <sub>H</sub> )                          |      |

| 7.2.3  | Packet Rx Valid High Register (Register 00A3 <sub>H</sub> )                        |      |

| 7.2.4  | Packet Rx Valid Low Register (Register 00A4 <sub>H</sub> )                         |      |

| 7.2.5  | Packet Rx Oversize High Register (Register 00A5 <sub>H</sub> )                     |      |

| 7.2.6  | Packet Rx Oversize Low Register (Register 00A6 <sub>H</sub> )                      |      |

| 7.2.7  | Packet Rx Undersize High Register (Register 00A7 <sub>H</sub> )                    |      |

| 7.2.8  | Packet Rx Undersize Low Register (Register 00A8 <sub>H</sub> )                     |      |

| 7.2.9  | Packet Rx CRC Register (Register 00A9 <sub>H</sub> )                               |      |

| 7.2.10 | Packet Rx CRC Oversize Register (Register 00AA <sub>H</sub> )                      |      |

| 7.2.11 | Packet Rx Fragment Register (Register 00AB <sub>H</sub> )                          |      |

| 7.2.12 | Packet Rx No SFD Register (Register 00AC <sub>H</sub> )                            | 117  |

### **Table of Contents**

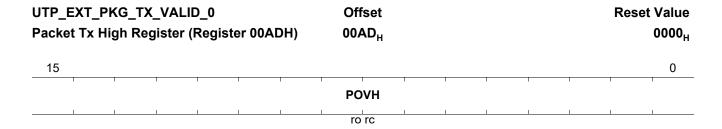

| 7.2.13  | Packet Tx High Register (Register 00AD <sub>H</sub> )           | 118 |

|---------|-----------------------------------------------------------------|-----|

| 7.2.14  | Packet Tx Low Register (Register 00AE <sub>H</sub> )            | 119 |

| 7.2.15  | Packet Tx Oversize High Register (Register 00AF <sub>H</sub> )  | 120 |

| 7.2.16  | Packet Tx Oversize Low Register (Register 00B0 <sub>H</sub> )   | 121 |

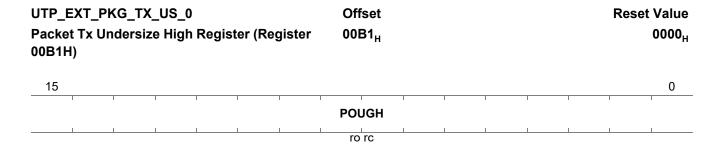

| 7.2.17  | Packet Tx Undersize High Register (Register 00B1 <sub>H</sub> ) | 122 |

| 7.2.18  | Packet Tx Undersize Low Register (Register 00B2 <sub>H</sub> )  | 123 |

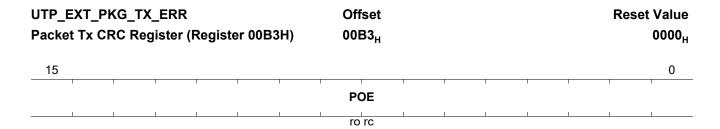

| 7.2.19  | Packet Tx CRC Register (Register 00B3 <sub>H</sub> )            | 124 |

| 7.2.20  | Packet Tx CRC Oversize Register (Register 00B4 <sub>H</sub> )   | 125 |

| 7.2.21  | Packet Tx Fragment Register (Register 00B5 <sub>H</sub> )       | 126 |

| 7.2.22  | Packet Tx No SFD Register (Register 00B6 <sub>H</sub> )         | 127 |

| 8       | Electrical Characteristics                                      | 128 |

| 8.1     | Absolute Maximum Ratings                                        |     |

| 8.2     | Operating Range                                                 |     |

| 8.3     | AC Characteristics                                              |     |

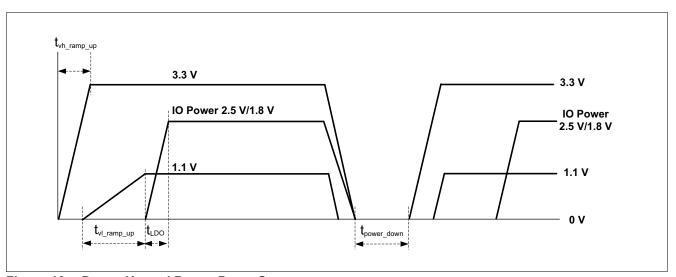

| 8.3.1   | Power Up and Power Down Sequence                                | 130 |

| 8.3.2   | Power Supply Rail Requirements                                  | 130 |

| 8.3.3   | Device Power Consumption                                        | 131 |

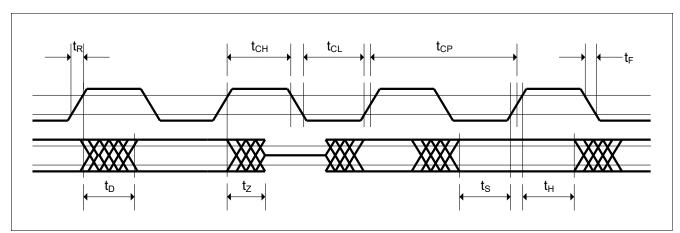

| 8.3.4   | MDIO Interface                                                  | 131 |

| 8.3.5   | RGMII Interface                                                 | 133 |

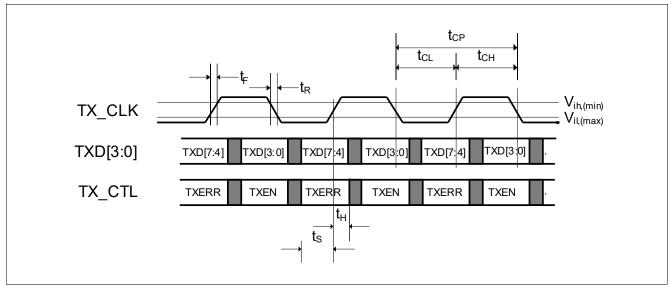

| 8.3.5.1 | Transmit Timing Characteristics                                 | 133 |

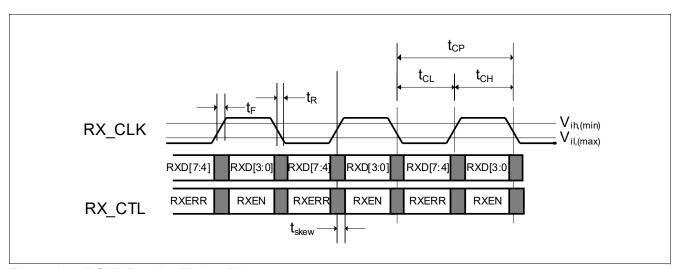

| 8.3.5.2 | Receive Timing Characteristics                                  | 134 |

| 8.3.6   | Crystal Specification                                           | 136 |

| 8.3.7   | External Clock Requirements                                     | 137 |

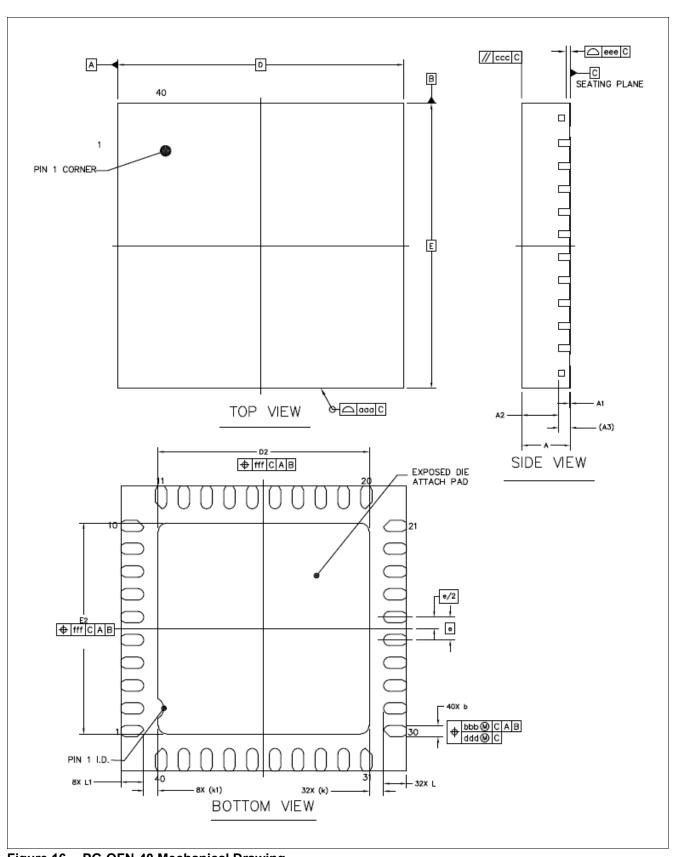

| 9       | Package Outline                                                 | 138 |

| 9.1     | Thermal Resistance                                              | 140 |

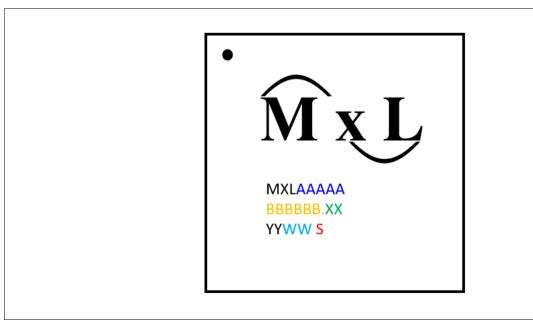

| 9.2     | Chip Identification and Ordering Information                    | 141 |

|         | Standards References                                            | 143 |

|         | Terminology                                                     | 144 |

### **List of Figures**

# **List of Figures**

| igure 1  | MxL86110 Block Diagram                | . 12 |

|----------|---------------------------------------|------|

| igure 2  | MxL86110 External Signals Overview    | . 14 |

| igure 3  | Pin Diagram for MxL86110              | . 15 |

| igure 4  | Near-End Loopback                     | . 25 |

| igure 5  | External Loopback                     | . 25 |

| igure 6  | Far-End PHY Loopback                  | . 26 |

| igure 7  | EEE Low Power Idle Sequence           | . 26 |

| igure 8  | Block Diagram of WoL Application      | . 27 |

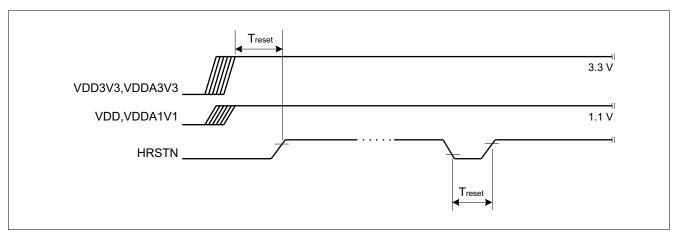

| igure 9  | Reset Timing Diagram                  | . 28 |

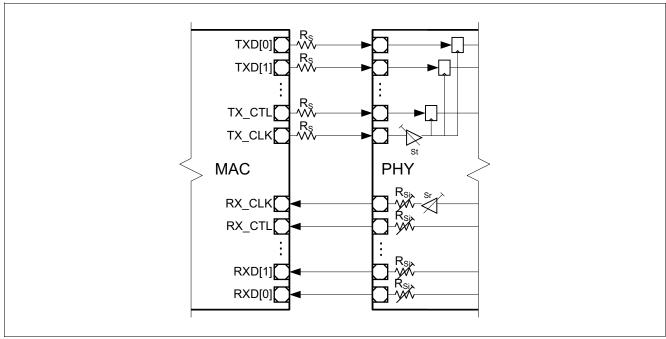

| igure 10 | Connection Diagram of RGMII           | . 29 |

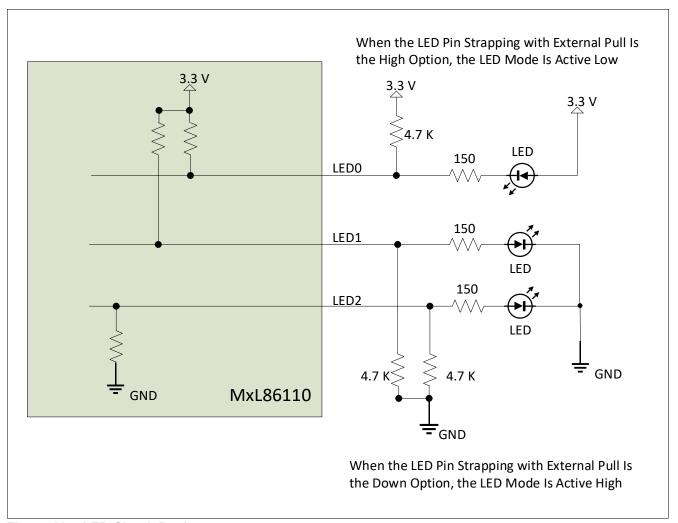

| igure 11 | LED Circuit Design                    | . 30 |

| igure 12 | Power Up and Power Down Sequence      | 130  |

| igure 13 | Timing Diagram for the MDIO Interface | 131  |

| igure 14 | RGMII Transmit Timing Diagram         | 133  |

| igure 15 | RGMII Receive Timing Diagram          | 134  |

| igure 16 | PG-QFN-40 Mechanical Drawing          | 139  |

| igure 17 | Chip Marking                          | 141  |

**List of Tables**

## **List of Tables**

| Table 1  | Abbreviations for Pin Type                               | . 16 |

|----------|----------------------------------------------------------|------|

| Table 2  | Abbreviations for Buffer Type                            | . 16 |

| Table 3  | Ethernet Media Interface Signals                         | . 17 |

| Table 4  | RGMII Interface Signals                                  | . 17 |

| Table 5  | LED Interface Signals                                    | . 19 |

| Table 6  | Management Interface Signals                             | . 20 |

| Table 7  | Miscellaneous Signals                                    | . 21 |

| Table 8  | Power Supply Pins                                        |      |

| Table 9  | Device Ground                                            | . 23 |

| Table 10 | Reset Timing Characteristics                             | . 28 |

| Table 11 | Pin Names Used for Pin Strapping                         | . 31 |

| Table 12 | Pin Strapping Configuration Description                  | . 31 |

| Table 13 | MMD Devices Present in MxL86110                          | . 35 |

| Table 14 | MDIO Register Access Type                                | . 36 |

| Table 15 | Registers Overview - Standard Management                 | . 37 |

| Table 16 | Registers Overview - PHY-specific Management Registers   | . 59 |

| Table 17 | MMD Register Access Type                                 | . 71 |

| Table 18 | Registers Overview - Standard PCS Registers              | . 72 |

| Table 19 | Registers Overview - Standard Auto-Negotiation Registers | . 75 |

| Table 20 | Extended Register Access Type                            | . 78 |

| Table 21 | Registers Overview - Common Extended Register            | . 79 |

| Table 22 | Registers Overview - UTP Extended Register               | 105  |

| Table 23 | Absolute Maximum Ratings                                 | 128  |

| Table 24 | Supply Voltage and Temperature                           | 129  |

| Table 25 | Sequence Timing Parameters                               | 130  |

| Table 26 | Device Power Consumption                                 | 131  |

| Table 27 | Maximum Device Power Consumption                         | 131  |

| Table 28 | Timing Characteristics of the MDIO Interface             | 132  |

| Table 29 | RGMII Transmit Timing Characteristics                    | 133  |

| Table 30 | RGMII Receive Timing Characteristics                     | 134  |

| Table 31 | Specification of the Crystal                             | 136  |

| Table 32 | Specification of the External Clock                      | 137  |

| Table 33 | PG-QFN-40 Mechanical Dimensions                          | 138  |

| Table 34 | Thermal Resistance                                       | 140  |

| Table 35 | Chip Marking Pattern                                     | 141  |

| Table 36 | Chip Ordering Information                                | 141  |

| Table 37 | Chip Specific Information                                | 142  |

**Preface**

### **Preface**

This Data Sheet describes the features and system architecture of the single port Gigabit Ethernet PHYs MxL86110C and MxL86110I.

Note: The device address map is considered as a flat address map implementation. No Mailbox functionality behind MDIO IF.

This document uses this synonym to simplify matters:

#### MxL86110

Synonym used for the Ethernet PHYs MxL86110C and MxL86110I

#### **Organization of this Document**

- Chapter 1, Product Overview

This chapter provides an overview.

- Chapter 2, External Signals

This chapter provides the external signals.

- Chapter 3, Functional Description

This description

This description

The first description description

The first description description

The first description descripti

- This chapter provides the function description.

- Chapter 4, MDIO and MMD Register Interface Description

This chapter describes the MDIO and MMD register format.

- Chapter 5, MDIO Registers Detailed Description

This chapter details the MDIO registers.

Chapter 6, MMD Registers Detailed Description

This chapter details the MDD registers.

Chapter 7, Extended Register Detailed Description

This chapter details the extended register.

- Chapter 8, Electrical Characteristics

- This chapter provides the electrical specifications.

- Chapter 9, Package Outline

This chapter provides information about the package.

- Standards References

- Terminology

Attention: MaxLinear only guarantees the behavior of the device based on documented registers.

The device does not offer any protection against access to other non-documented addresses over the MDIO interface.

### 1 Product Overview

The MxL86110 is a low power Ethernet PHY transceiver integrated circuit following the IEEE 802.3 [1] standard. It offers a cost-optimized solution that is well-suited for routers, switches, and home gateways. It performs data transmission on an Ethernet twisted pair copper cable of category CAT5e or higher. The MxL86110 supports 1000, 100, and 10 Mbit/s data rates.

On the Ethernet twisted pair interface, the MxL86110 is compliant with the 1000BASE-T (IEEE802.3 Clause 40), 100BASE-TX (IEEE 802.3 Clause 25), and 10BASE-Te (IEEE 802.3 Clause 14) standards defined by the IEEE 802.3 see [1] for more information. This interface supports the Energy-Efficient Ethernet (EEE) feature in accordance with IEEE802.3 [1] to reduce idle mode power consumption. Power saving at the system level is also possible with the Wake-on-LAN feature. A low-EMI line driver with integrated termination facilitates PCB design.

The MxL86110 supports a standard MDIO management interface as defined in IEEE 802.3 Clause 22 and Clause 45 [1]. The MDIO serial interface operates with a clock running up to 12.5 MHz. This allows a management entity (the external chip implementing the MAC) to access standard MDIO / MMD registers to control the MxL86110 behavior, or to read the link status. In addition, vendor specific register banks allow MxL86110-specific configuration of LED, and Wake-on-LAN features. The MDIO and MMD registers are documented in **Chapter 5** and **Chapter 6**, respectively. The MxL86110 is also configurable via pin strapping.

The MxL86110 can drive up to three LEDs. Each LED is independently programmable to indicate the link speed, and traffic activity. Several indication schemes are selectable.

A DC/DC converter is integrated within the MxL86110. A single external power supply of 3.3 V is sufficient to power the chip, with the internal DC/DC converter generating 1.1 V to supply the low voltage domains. External supply of both 3.3 V and 1.1 V is also an option.

The MxL86110 is available in a Quad Flat Non-leaded package (PG-QFN-40). It therefore provides an ideal solution for footprint-sensitive applications such as SFP copper modules or Ethernet Controllers. Furthermore, the MxL86110 design supports a reduced external bill of materials, for example through the integration of termination resistors at both the MDI and MII. The CLKOUT pin can optionally be used to provide a 25 MHz reference clock, allowing for multiple PHY devices to be cascaded while using only one crystal.

The MxL86110 uses a PG-QFN-40 package which is 5 x 5 mm in size.

The MxL86110 has a built-in switching regulator for 1.1 V core power.

The MxL86110 has a built-in LDO providing 2.5/1.8 V power for the RGMII I/O interface.

#### 1.1 Features

This section provides an overview of the features supported by the MxL86110.

#### **Communication Interfaces**

- The multiple speed, single-port Ethernet PHY interface to the twisted pair cable supports:

- Ethernet modes and standards: 1000BASE-T (IEEE 802.3), 100BASE-TX (IEEE 802.3) and 10BASE-Te (IEEE 802.3)

- Ethernet twisted pair copper cable of category CAT5 or higher

- Low EMI voltage mode line driver with integrated termination resistors

- Transformerless Ethernet for backplane applications

- Auto-Negotiation (ANEG) with extended next page support

- Auto-MDIX and polarity correction

- Auto-Downspeed (ADS)

- Energy-Efficient Ethernet (EEE) and power down mode

- Wake-on-LAN (WoL)

- 10k byte jumbo frame support.

- RGMII Interface

- The management interface supports the communication between the Station Management Entity (STA) and the MxL86110 using:

- An MDIO slave interface that provides access to the standard registers in the MMD as described in IEEE 802.3 Clause 22 and Clause 45 [1] and listed in Chapter 5 and Chapter 6

- An MDIO interface clock of up to 12.5 MHz

- Three MDIO message frame types as described in IEEE 802.3: Clause 22, Clause 22 Extended, and Clause 45 [1]

#### LED Interface, which supports:

- · Up to three LEDs

- Single color LEDs

- Connection of LED to ground or 3.3 V

- Several LED indication schemes (link/activity, link speed)

- Configuration of LED indication via Extended Registers

Supports one interrupt output to external controller.

#### **Clocking and Timing Features**

25 MHz crystal operation

#### **Power Supply**

- Single 3.3 V power supply, when using the integrated switching regulator to DC/DC converter to generate the 1.1 V power supply rail

- If the internal integrated DC/DC converter is not used, an additional 1.1 V supply must be provided externally

- Built-in LDO for RGMII IO power 2.5/1.8 V

### 1.2 Block Diagram

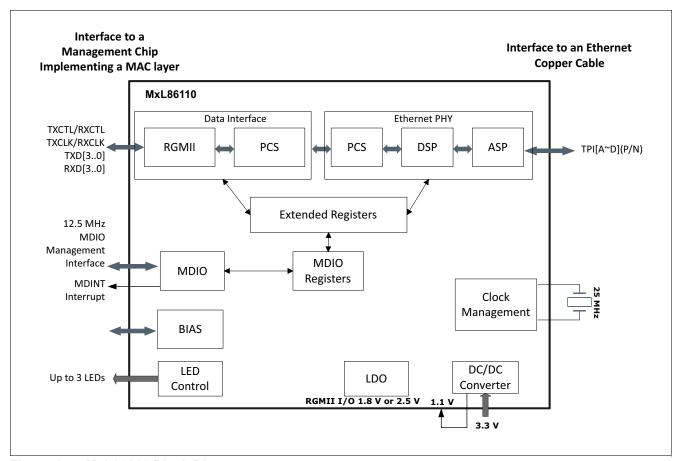

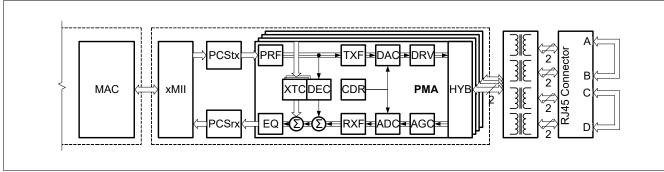

Figure 1 shows the block diagram of the MxL86110. The main interfaces are:

- Data interface to a MAC processor, using RGMII

- · Slave control interface driven by a MAC processor, using MDIO slave

- Interrupt signal MDINT allowing the MxL86110 to notify the MAC processor about a change of status

- LED control

- · Twisted Pair Interface (TPI)

Figure 1 MxL86110 Block Diagram

## 1.3 Target Applications

- Gateways

- Routers

- Wi-Fi access points

- Set-top-boxes

- IP-phones

- Digital TVs

- Ethernet switches

- NAS

- DVD Players

- Game consoles

- Printers

- Office machines

- Industrial PCs

- IoT devices

- PoE applications

## 2 External Signals

This chapter describes the signal mapping to the package.

### 2.1 Overview

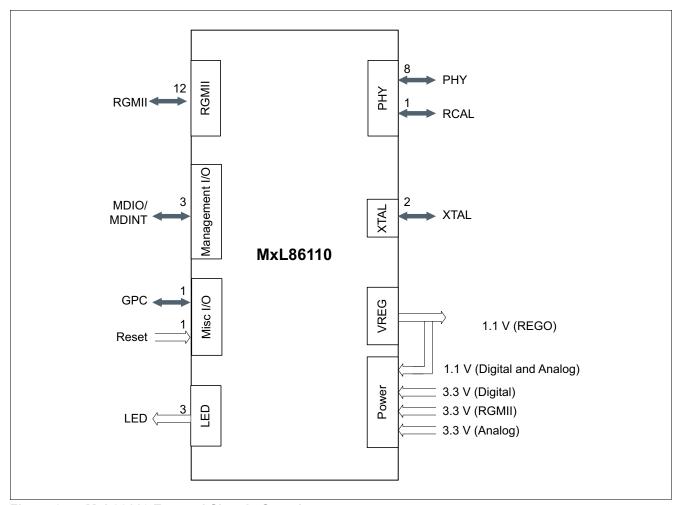

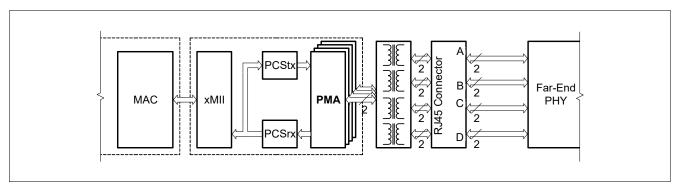

Figure 2 provides an overview of the external interfaces of the MxL86110.

Figure 2 MxL86110 External Signals Overview

### 2.2 External Signal Description

This section provides the pin diagram, abbreviations for pin types and buffer types, as well as tables describing the input and output signals.

### 2.2.1 Pin Diagram

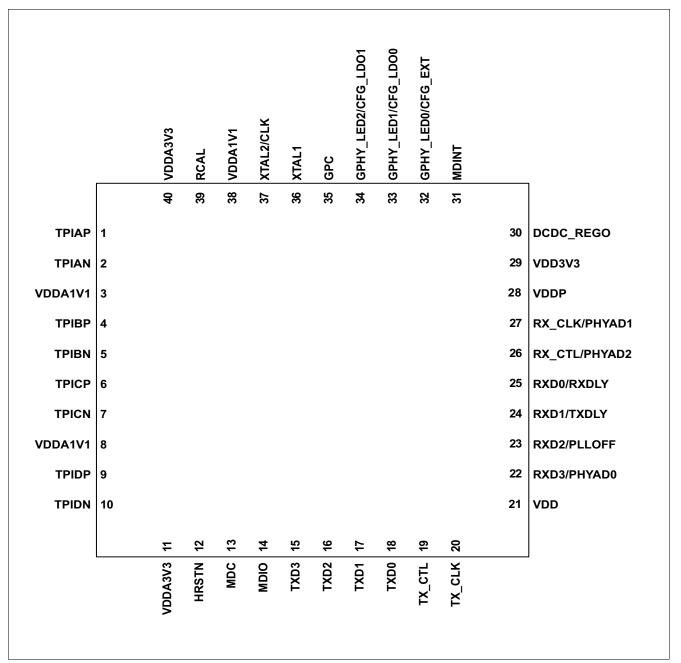

Figure 3 shows the pin layout for the MxL86110 package.

Figure 3 Pin Diagram for MxL86110

### 2.2.2 Abbreviations

Abbreviations that are used in the signal tables are summarized in Table 1 and Table 2.

Table 1 Abbreviations for Pin Type

| Abbreviations | Description                                       |  |  |  |  |

|---------------|---------------------------------------------------|--|--|--|--|

| I             | Input only, digital levels                        |  |  |  |  |

| О             | Output only, digital levels                       |  |  |  |  |

| I/O           | Bidirectional input/output signal, digital levels |  |  |  |  |

| Al            | Input only, analog levels                         |  |  |  |  |

| AO            | Output only, analog levels                        |  |  |  |  |

| AI/O          | Bidirectional, analog levels                      |  |  |  |  |

| PWR           | Power                                             |  |  |  |  |

| GND           | Ground                                            |  |  |  |  |

### Table 2 Abbreviations for Buffer Type

| Abbreviations Description |                                                                     |  |  |

|---------------------------|---------------------------------------------------------------------|--|--|

| A                         | Analog characteristics, see the AC/DC specification for more detail |  |  |

| GND                       | Ground                                                              |  |  |

| OD                        | Open Drain                                                          |  |  |

| PU                        | Internal pull-up resistor                                           |  |  |

| PD                        | Internal pull-down resistor                                         |  |  |

### 2.2.3 Input/Output Signals

A detailed description of all the pins is given in Table 3 to Table 7.

In **Table 3** to **Table 7**, the signal names highlighted in bold are the same as the pin name. Signal names are provided in bold. The primary function is listed first and then alternate functions.

#### 2.2.3.1 Ethernet Media Interface

Table 3 describes the Ethernet Media Interface's TPI pins which uses pins 1-10.

Table 3 Ethernet Media Interface Signals

|          |               |                 | U      |                                                 |

|----------|---------------|-----------------|--------|-------------------------------------------------|

| Pin No.  | Name          | Pin             | Buffer | Function                                        |

|          |               | Type            | Type   |                                                 |

| Ethernet | Port Ethernet | Media Interface | •      |                                                 |

| 1        | TPIAP         | AI/AO           | Α      | Twisted Pair Transmit/Receive Positive/Negative |

| 2        | TPIAN         | AI/AO           | Α      |                                                 |

| 4        | TPIBP         | AI/AO           | Α      |                                                 |

| 5        | TPIBN         | AI/AO           | Α      |                                                 |

| 6        | TPICP         | AI/AO           | Α      |                                                 |

| 7        | TPICN         | AI/AO           | Α      |                                                 |

| 9        | TPIDP         | AI/AO           | Α      |                                                 |

| 10       | TPIDN         | AI/AO           | Α      |                                                 |

#### 2.2.3.2 RGMII

Table 4 describes the RGMII interface-related pins which uses pins 15-20 and 22-27.

Table 4 RGMII Interface Signals

| Pin No.  | Name            | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                 |

|----------|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RGMII In | terface Signals |             | <u> </u>       |                                                                                                                                          |

| 15       | TXD3            | I           | PD             | RGMII: Transmit Data Bit 3 This pin carries bit 3 of the TXD[3:0] RGMII transmit data vector. It is synchronous with TXC.                |

| 16       | TXD2            | I           | PD             | RGMII: Transmit Data Bit 2 This pin carries bit 2 of the TXD[3:0] RGMII transmit data vector. It is synchronous with TXC.                |

| 17       | TXD1            | I           | PD             | RGMII: Transmit Data Bit 1 This pin carries bit 1 of the TXD[3:0] RGMII transmit data vector. It is synchronous with TXC.                |

| 18       | TXD0            | I           | PD             | RGMII: Transmit Data Bit 0 This pin carries bit 0 of the TXD[3:0] RGMII transmit data vector. It is synchronous with TXC.                |

| 19       | TX_CTL          | I           | PD             | RGMII: Transmit Control This pin is the transmit control signal for the TXD[3:0] RGMII transmit data vector. It is synchronous with TXC. |

Table 4 RGMII Interface Signals (cont'd)

| Pin No. | Name              | Pin      | Buffer | Function                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                   | Type     | Type   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20      | TX_CLK            | <b>I</b> | PD     | RGMII: Transmit Clock The TXC signal is a continuous clock signal and provides the timing reference for the transfer of TX_EN_CTL and TXD[3:0]. The nominal frequency of this clock is 125 MHz for 1000 Mbit/s, 25 MHz for 100 Mbit/s, and 2.5 MHz for 10 Mbit/s. Depending on the speed selection, this clock is assumed to be properly adjusted by the MAC. The frequency deviation is assumed to be smaller than +/- 50 ppm. |

| 22      | RXD3<br>/PHYAD0   | I/O      | PD     | RGMII: Receive Data Bit 3 This pin carries bit 3 of the RXD[3:0] RGMII receive data vector. It is synchronous with RXC. PHYAD0: This pin reads in soft pin-strapping information during reset.                                                                                                                                                                                                                                  |

| 23      | RXD2<br>/PLLOFF   | I/O      | PD     | RGMII: Receive Data Bit 2 This pin carries bit 2 of the RXD[3:0] RGMII receive data vector. It is synchronous with RXC. PLLOFF: This pin reads in soft pin-strapping information during reset.                                                                                                                                                                                                                                  |

| 24      | RXD1<br>/TXDLY    | I/O      | PD     | RGMII: Receive Data Bit 1 This pin carries bit 1 of the RXD[3:0] RGMII receive data vector. It is synchronous with RXC.  TXDLY: This pin reads in soft pin-strapping information during reset.                                                                                                                                                                                                                                  |

| 25      | RXD0<br>/RXDLY    | I/O      | PD     | RGMII: Receive Data Bit 0 This pin carries bit 0 of the RXD[3:0] RGMII receive data vector. It is synchronous with RXC.  RXDLY: This pin reads in soft pin-strapping information during reset.                                                                                                                                                                                                                                  |

| 26      | RX_CTL<br>/PHYAD2 | I/O      | PD     | RGMII: Receive Control This is the receive control signal driven by the PHY, and which is synchronous with RXC. The signal encodes the RX_DV and RX_ER signals of the GMII. PHYAD2: This pin reads in soft pin-strapping information during reset.                                                                                                                                                                              |

| 27      | RX_CLK<br>/PHYAD1 | I/O      | PD     | RGMII: Receive Clock The RXC signal is a continuous clock signal and provides the timing reference for the transfer of RX_EN_CTL and RXD[3:0]. The nominal frequency of this clock is 125 MHz for 1000 Mbit/s, 25 MHz for 100 Mbit/s and 2.5 MHz for 10 Mbit/s. The frequency deviation is smaller than +/-50 ppm. PHYAD1: This pin reads in soft pin-strapping information during reset.                                       |

### 2.2.3.3 LED Interface

**Table 5** describes the LED interface-related pins which allow external LEDs to be connected to the MxL86110C/MxL86110I to indicate the status of the Ethernet PHY interfaces. The LED interface uses pins 32-34.

Table 5 LED Interface Signals

| Pin No.  | Name                   | Pin<br>Type | Buffer<br>Type | Function                                                                                                                            |  |  |  |

|----------|------------------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LED Sigi | LED Signals            |             |                |                                                                                                                                     |  |  |  |

| 32       | GPHY_LED0<br>/CFG_EXT  | I/O         | PU             | GPHY LED0 The LED control output drives single color LEDs. CFG_EXT: This pin reads in soft pin-strapping information during reset.  |  |  |  |

| 33       | GPHY_LED1<br>/CFG_LDO0 | I/O         | PU             | GPHY LED1 The LED control output drives single color LEDs. CFG_LD00: This pin reads in soft pin-strapping information during reset. |  |  |  |

| 34       | GPHY_LED2<br>/CFG_LDO1 | 0           | PD             | GPHY LED2 The LED control output drives single color LEDs. CFG_LDO1: This pin reads in soft pin-strapping information during reset. |  |  |  |

## 2.2.3.4 Management Interfaces

Table 6 describes the MIDO slave interface pins which uses pins 13, 14, and 31

Table 6 Management Interface Signals

| Pin No. | Name          | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                          |

|---------|---------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIO SI | ave Interface |             |                |                                                                                                                                                                   |

| 13      | MDC           | I           | PD             | MDIO Slave Clock The external controller host, also called STA by the IEEE, acts as clock master and provides the serial clock of up to 12.5 MHz on this input.   |

| 14      | MDIO          | I/O         | PU             | MDIO Slave Data Input/Output The external controller host uses this signal to address internal registers and to transfer data to and from the internal registers. |

| 31      | MDINT         | 0           | OD             | MDIO Interrupt The MDINT signal is used to send an interrupt to an external MAC SoC acting as station manager (STA).                                              |

## 2.2.3.5 Miscellaneous Signals

Table 7 lists miscellaneous signals required by the device.

Table 7 Miscellaneous Signals

| Pin No.  | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                   |

|----------|------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset an | d Clocking | ·           |                |                                                                                                                                                                                                                                            |

| 37       | XTAL2      | AO          | A              | Crystal: Oscillator Output  A crystal must be connected between XTAL1 and XTAL2.  Additional load capacitances must also tie both pins to GND.                                                                                             |

|          | CLK        | I           |                | Clock: Clock Input The clock must have a frequency accuracy of ±50 ppm. When connecting an external 25 MHz oscillator or clock from another device to XTAL2 pin, XTAL1 must be tied to GND.                                                |

| 36       | XTAL1      | Al          | A              | Crystal: Oscillator Input A crystal must be connected between XTAL1 and XTAL2. Additional load capacitances must also tie both pins to GND.                                                                                                |

| 35       | GPC        | 0           |                | General Purpose Clock  1. This is the reference clock generated from the internal PLL. This pin should be kept floating if the clock is not used by the MAC.  2. UTP recovery receive clock for Sync Ethernet.  3. 25 MHz reference clock. |

| 12       | HRSTN      | I           | PU             | Hardware Reset Asynchronous active low device reset.                                                                                                                                                                                       |

### 2.2.3.6 Power Supply

This section specifies the power supply pins. The device is supplied by to supply rails,  $V_{HIGH}$  (3.3 V) and  $V_{LOW}$  (1.1 V). The  $V_{LOW}$  domain can either be supplied externally, or self-generated by the internal DC/DC Selecting Voltage Regulator (SVR) converter, which converts the VDD3V3 supply into DCDC\_REGO output. In the external supply configuration, the DCDC\_REGO output pins are not connected (NC). In the internal DC/DC SVR converter configuration, the DCDC\_REGO output pins are connected back to the  $V_{LOW}$  supply inputs.

| Table 8 | Power Supply Pins |

|---------|-------------------|

|---------|-------------------|

| I able 8 | Power Supp       | ly Pins     |                |                                                                                                                                                                                                                                                                                                                                                        |

|----------|------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | Name             | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                               |

| Power S  | upply Pins       |             |                |                                                                                                                                                                                                                                                                                                                                                        |

| 11, 40   | VDDA3V3          | PWR         |                | High Voltage Domain Supply $V_{HIGH}$<br>These are the input power pins for the analog front end in the high voltage domain. They must be supplied with a nominal voltage of $V_{DDA3V3} = 3.3 \text{ V}$ .                                                                                                                                            |

| 3, 8, 38 | VDDA1V1          | PWR         |                | Low Voltage Domain Supply V <sub>LOW</sub> These are the input power supply pins for the low voltage domain. These pins must be supplied with a nominal voltage of 1.1 V. When the internal DC/DC SVR converter is used, they must be connected to the output of the converter DCDC_REGO.                                                              |

| 28       | VDDP             | PWR         |                | Configurable MDIO Pin Voltage Domain Supply The voltage domains for the digital RGMII I/O and MDC/MDIO are controlled by the pins CFG_EXT, CFG_LDO0, and CFG_LDO1. Refer to Section 3.16 for the settings. No matter whether the I/O pin power form external or internal, a bulk capacitor and a decoupling capacitor should be connected to this pin. |

| 21       | VDD              | PWR         |                | Core Voltage Domain Supply $V_{LOW}$<br>This is the group of supply pins for the core digital voltage domain. This pin must be supplied with a nominal voltage of $V_{DD} = 1.1 \text{ V}$ . When the internal DC/DC SVR converter is used, these pins must be connected to the output of the converter DCDC_REGO.                                     |

| 29       | VDD3V3           | PWR         |                | Power Supply $V_{HIGH}$<br>This pin must be supplied with a nominal voltage of $V_{DD3V3} = 3.3 \text{ V}$ .                                                                                                                                                                                                                                           |

| 30       | DCDC_REGO        | PWR         |                | Internal DC/DC SVR Converter Output The connection circuitry for the internal DCDC SVR $V_{LOW}$ supply option and the external $V_{LOW}$ supply option are described in Figure 16.                                                                                                                                                                    |

| Ethernet | Port Calibration | 1           |                |                                                                                                                                                                                                                                                                                                                                                        |

| 39       | RCAL             | AI/AO       | А              | Calibration of GPHY Ethernet Port Connect a high precision resistor of 2.49 kΩ ±1% to GND                                                                                                                                                                                                                                                              |

### Table 9 Device Ground

| Pin No.            | Name | Pin<br>Type | Buffer<br>Type | Function              |

|--------------------|------|-------------|----------------|-----------------------|

| EPAD <sup>1)</sup> | VSS  | GND         |                | General device ground |

<sup>1)</sup> The EPAD is the exposed pin on the bottom of the package. This pin must be properly connected to the ground plane of the PCB.

### 3 Functional Description

This chapter describes the functions available to the MxL86110.

### 3.1 Management Interface

The status and control registers of the device are accessible through the MDIO and MDC serial interface. The functional and electrical properties of this management interface comply with IEEE 802.3, Section 22 and also support MDC clock rates up to 12.5 MHz.

### 3.2 Auto-Negotiation (ANEG)

The MxL86110 negotiates its operation mode using the ANEG mechanism according to IEEE 802.3 Clause 28 over the copper media. ANEG supports choosing the mode of operation automatically by comparing its own abilities and received abilities from link partner. The advertised abilities include:

- Speed: 10/100/1000Mbps

- Duplex mode: full-duplex and/or half-duplex

ANEG is initialized when these scenarios occur:

- · Power-up/Hardware/Software reset

- ANEG restart

- Transition from power down to normal operation of the port

- · Link down

ANEG is enabled for MxL86110 by default, and can be disabled by software control.

### 3.3 Polarity Detection and Auto Correction

The MxL86110 can detect and correct two types of cable errors.

- Swapped pairs within the UTP cable:

- Pair 0 and 1, and/or pair 2 and 3.

- · Swapped wires within a pair.

### 3.4 Loopback Mode

The MxL86110 supports several test loops to support system integration.

#### 3.4.1 Near-End Test Loops

Digital loopback provides the ability to loop transmitted data back to the receiver using digital circuitry in the MxL86110.

The near-end test loops are used to verify system integration of an MxL86110 device. They allow for closed loopback of data and signals at different Open Systems Interconnection (OSI) reference layers. **Section 3.4.2** and **Section 3.4.3** describe these loopback functions in descending order of OSI abstraction layer. Digital loopback is set via STD\_CTRL.LB = 1<sub>B</sub>. See **Section 5.1.1**.

Figure 4 Near-End Loopback

### 3.4.2 External Loopback

The MxL86110 supports an external loopback with help of a physical connection at the RJ45 connector as shown in **Figure 5**. This allows a complete Tx -> Rx cable loopback.

25

Figure 5 External Loopback

Note: External loopback is set via UTP\_EXT\_10BT\_DBG.ELB. See Section 7.2.

### 3.4.3 Far-End PHY Loopback

The Far-End loopback mode connects the MDI Rx path to the MDI Tx path close to RGMII interface as shown in **Figure 6**. With this function the Far-End PHY can detect the proper connectivity.

Figure 6 Far-End PHY Loopback

Note: Remote PHY loopback is set via COM\_EXT\_MISC\_CFG.RLBP. See Section 7.2.

### 3.5 Energy Efficient Ethernet (EEE)

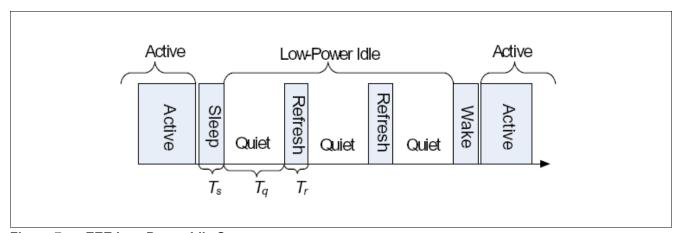

The IEEE 802.3 standard [1] describes the EEE operation that is supported by the MxL86110. EEE is supported in the various speeds of 100BASE-TX and 1000BASE-T. The general idea of EEE is to save power during periods of low link utilization. Instead of sending active idle data, the transmitters are switched off for a short period of time. This is called the quiet period in the standard. The link is kept active by means of a frequent refresh cycle initiated by the PHY itself while in the low power state. This sequence is repeated until a wake request is generated by one of the link partner MACs.

Figure 7 EEE Low Power Idle Sequence

### 3.6 Synchronous Ethernet (SyncE)

The MxL86110 provides Synchronous Ethernet (SyncE) support when the device is operating in 1000BASE-T and 100BASE-TX on the transmission media. The GPC pin can be assigned to output the recovered clock.

The MxL86110 allows a SyncE interface to support transportation of a source-referable clock from a clock master to clock clients. This is supported in 1000BASE-T and 100BASE-T mode on the TPI.

- In 1000BASE-T, the GPC outputs the recovered clock from PHY<->PHY.

- In slave mode, the GPC outputs the recovered clock from MDI.

- In master mode, the GPC outputs the clock from local free running PLL.

When the GPC pin is assigned to output the recovered clock from the PHY and the PHY is configured for 1000BASE-T mode, the function of the GPC varies depending upon the current PHY mode.

- When the PHY is in slave mode, the GPC outputs the recovered clock from the MDI.

- · When the device is in master mode, the GPC outputs the clock based on the local free run PLL.

#### 3.7 Wake-On-LAN (WoL)

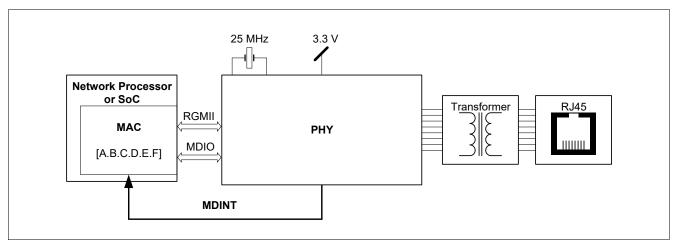

The MxL86110 supports WoL. The MxL86110 generates an interrupt to an external controller when it detects special WoL Ethernet packets. This allows the controller to enter into sleep mode when there is no Ethernet traffic to process, and be woken up when traffic starts. WoL packets are detected at all link speeds. **Figure 8** shows this scenario. The specific frame contains a specific data sequence located anywhere inside the packet. The 48-bit address is set using the COM\_EXT\_MAC\_ADDR\_CFG1, COM\_EXT\_MAC\_ADDR\_CFG2, and COM\_EXT\_MAC\_ADDR\_CFG3 registers. See **Section 7.1**.

Figure 8 Block Diagram of WoL Application

The most commonly used WoL packet is called a magic packet. A magic packet contains the MAC address of the device to be woken up.

### 3.8 Link Down Power Saving (Sleep Mode)

The MxL86110 supports link down power saving, also called sleep mode. The MxL86110 enters sleep mode after around 40 seconds if no signals are received over the Ethernet cable.

In sleep mode, the MxL86110 disables almost all circuits, nevertheless access by MDC/MDIO interface remains available.

Once signals are detected on an Ethernet cable, the MxL86110 exits sleep mode automatically.

#### 3.9 Interrupt

The MxL86110 provides an active low interrupt output signal (MDINT) based on change of the PHY status. Every interrupt condition is mapped to the read-only general interrupt status register by the read-only general interrupt status register. See **Section 5.2** for more information.

The interrupts can be individually enabled or disabled by setting or clearing bits in the interrupt enable register **Section 5.2.** See PHY\_IMASK **Section 5.2.3**.

The MDINT signal is used to send an interrupt to an external MAC SoC acting as station manager (STA). The STA can program its sensitivity to specific events using the PHY\_IMASK register. The MDINT event is then raised when the event occurs. The STA can read which type of event occurred in the PHY\_ISTAT register. Upon reading of PHY\_ISTAT by the STA, the MDINT is deasserted by the MxL86110.

27

Note: The interrupt of the MxL86110 is a level-triggered mechanism.

### 3.10 **Reset**

The MxL86110 has a hardware reset (HRSTN) pin. The HRSTN signal must be active for at least 10 ms after power-up. After the HRTSN is released, the MxL86110 latches the input values on the strapping pins to configure the device settings. This is useful for configuring the device in applications where MDIO access is unavailable. After a hardware reset, there is a 100 ms MDIO access delay to complete MxL86110 internal initialization.

Figure 9 Reset Timing Diagram

Table 10 Reset Timing Characteristics

| Symbol             | Description                                                                              | Min. | Тур. | Max. | Units |

|--------------------|------------------------------------------------------------------------------------------|------|------|------|-------|

| T <sub>reset</sub> | The amount of time to allow all power rails to stabilize before releasing HRSTN to high. | 10   | -    | -    | ms    |

| T <sub>reset</sub> | The minimum amount of time for a reset signal to be recognized.                          | 10   | -    | -    | ms    |

#### 3.11 PHY Address

The MxL86110 offers the ability to configure the PHY address from the pins PHYAD1/PHYAD2. In addition, MxL86110 supports broadcast address 0 on the MDIO bus. This feature enables PHY to always respond to MDIO access. It is controlled via the COM\_EXT\_RGMII\_MDIO\_CFG register. See **Section 7.1** for more information.

The MxL86110 supports the option to configure a dedicated broadcast PHY address.

#### 3.12 RGMII Interface

The RGMII interface implements a MAC interface which is usable for all supported speeds (10/100/1000 Mbit/s).

The transfer of data between the MAC and PHY devices is handled via a clock signal, a control signal, and a four bit data vector in both the transmit and receive directions. The clock signal is always driven by the signal source, which is the MAC in the transmit direction and PHY in the receive direction. The control and data signals change with both the rising and falling edges of the driving clock.

The nominal driving clock frequency at 1000 Mbit/s data speeds is 125 MHz. Lower speeds of 100 Mbit/s and 10 Mbit/s use a clock frequency of 25 MHz and 2.5 MHz respectively. At these lower speeds, the higher half of the data octet is empty and the signals on TXD[3:0] and RXD[3:0] are duplicated.

Figure 10 Connection Diagram of RGMII

#### 3.13 LED Interface

The LED interface is controllable by two methods: by the PHY or manually controlled. The LED interface provides up to three LEDs to provide visual indication of the link speed, duplex, and link status. The LEDs are programmable by the MDIO interface via direct register access. **Figure 11** shows the LED circuit design.

Figure 11 LED Circuit Design

### 3.14 MDINT Pin Usage

The MDINT pin is used to notify the network processor, or SoC, of both interrupt and WoL events. For general use, indication of a WoL event is also integrated into one of the interrupt events which is triggered when any specified WoL event occurs.

### 3.15 Power Supply Rails

The MxL86110 requires only one external supply rail of 3.3 V. The device has an integrated SVR which generates the 1.1 V rail, as well as an LDO to adapt to different RGMII levels (either 2.5 / 1.8 V).

The RGMII I/O voltage level is set via external strapping.

When the integrated SVR is not used, the MxL86110 can be powered by a 3.3 V and 1.1 V dual power supply. See **Section 8.2** for more information on the electrical characteristics of the power supply. In external supply mode, the DCDC\_REGO output pins are left unconnected. The integrated SVR converter is able to be switched off after power up.

### 3.16 Configuration by Pin Strapping

The MxL86110 device can be configured by means of pin strapping several pins. The pin strapping configurations are captured during the chip power-on sequence, until the reset initialization is complete. The pin strap values can be set to logical high or low by connecting the corresponding pin via an external 1 k $\Omega$  resistor to either ground or the VDD domain supply for the pin strapping pins. For example, GPHY\_LED0/1/2 connects to either ground or 3.3 V and RXD3/2/1/0/RX\_CLK/RXCTL connects to either ground or the VDDP domain.

The pin strap mapping is described in Table 11 and Table 12.

Table 11 Pin Names Used for Pin Strapping

| Pin Name  | Pin Number | Configuration Item Description |  |

|-----------|------------|--------------------------------|--|

| RXD3      | 22         | PS_PHY_MADDR(0)                |  |

| RXD2      | 23         | PLLOFF                         |  |

| RXD1      | 24         | TXDLY                          |  |

| RXD0      | 25         | RXDLY                          |  |

| RX_CTL    | 26         | PS_PHY_MADDR(2)                |  |

| RX_CLK    | 27         | PS_PHY_MADDR(1)                |  |

| GPHY_LED0 | 32         | CFG_EXT                        |  |

| GPHY_LED1 | 33         | CFG_LDO0                       |  |

| GPHY_LED2 | 34         | CFG_LDO1                       |  |

Table 12 Pin Strapping Configuration Description

| Pin Strapping Signals | Description                                                                     |

|-----------------------|---------------------------------------------------------------------------------|

| PS_PHY_MADDR(2:0)     | MDIO PHY Address                                                                |

|                       | A high level means a logical 1 and low level means a logical 0.                 |

| PLLOFF                | PLL off Configuration During Sleep Mode                                         |

|                       | 0 <sub>B</sub> PLL is on during sleep mode.                                     |

|                       | 1 <sub>B</sub> PLL is off during sleep mode.                                    |

| TXDLY                 | RGMII Transmit Clock Timing Control                                             |

|                       | 0 <sub>B</sub> No additional delay on TX_CLK.                                   |

|                       | 1 <sub>B</sub> Enable 2 ns delay on TX_CLK when TX_CLK is 125 MHz or 8 ns delay |

|                       | on TX_CLK when TX_CLK is 25 MHz/2.5 MHz.                                        |

| RXDLY                 | RGMII Receiver Clock Timing Control                                             |

|                       | 0 <sub>B</sub> No additional delay on RX_CLK.                                   |

|                       | 1 <sub>B</sub> Enable 2 ns delay on RX_CLK when RX_CLK is 125 MHz or 8 ns delay |

|                       | on RX_CLK when RX_CLK is 25 MHz/2.5 MHz.                                        |

Table 12 Pin Strapping Configuration Description

| Pin Strapping Signals | Description                                                                                                                                                                                                          |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFG_EXT               | External Power Source Mode Configuration  0 <sub>B</sub> Use the integrated LDO to supply the RGMII/MDIO I/O pin.  1 <sub>B</sub> Use an external power source on VDDP for the RGMII/MDIO I/O pin.                   |

| CFG_LDO(1:0)          | Configuration of Integrated LDO voltage This is the voltage level configuration for supplying the RGMII/MDIO I/O pin.  00 <sub>B</sub> Reserved  01 <sub>B</sub> 2.5 V  10 <sub>B</sub> 1.8 V  1x <sub>B</sub> 1.8 V |

**MDIO** and **MMD** Register Interface Description

### 4 MDIO and MMD Register Interface Description

This chapter describes the MDIO and MMD registers, which are standardized by IEEE 802.3 [1], and available to support the MxL86110 feature set. After power-on, the MxL86110 resets the MDIO and MMD registers to default values that are sufficient to operate without specific programing.

All the register definitions, behaviors, and fields are strictly compliant with the IEEE 802.3 [1]. There are PHY specific registers which are not referenced in IEEE 802.3, which can be found in **Section 5.2**. These allow custom functions related to the MxL86110.

#### 4.1 Definitions

These acronyms are used in the IEEE 802.3 standard and commonly used in the Ethernet technical domain:

- STA: Station Management. A host connected to the MDIO interface. STAs are generally Media Access Controllers (MACs). The STA drives the MDIO bus as a clock master and the MxL86110 is MDIO slave.

- Host: Used as a synonym of STA in this document.

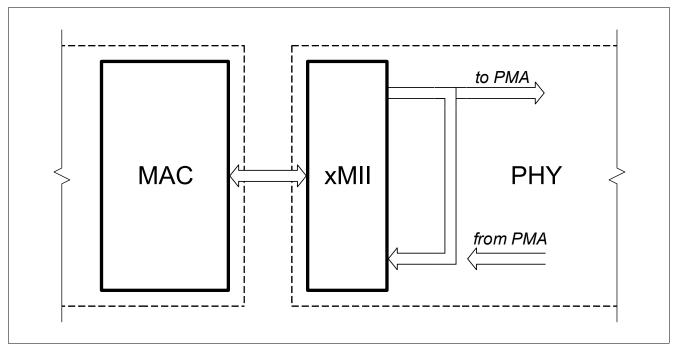

- PHY: Physical Layer. In the MxL86110 this encompasses Analog Signal Processing, Digital Signal Processing, and Physical Coding Sublayer (PCS). The PHY contains several sub-layers that are individually manageable entities known as MDIO manageable devices (MMDs).

- MMD: MDIO Manageable Device. The list of MMDs available in the MxL86110 is in Section 4.3.

- **Device**: In the context of MDIO/MMD registers, a device is a register bank grouped by logical sub-layers of the PHY layer.

- Clause: Refers to a particular section of the IEEE 802.3 standard [1]. In particular Clause 22 describes MDIO device 0, and Clause 45 describes the other MMDs.

- MII: Media Independent Interface. This encompasses the MDIO as well as the (G)MII as described in Clause 22. STD registers in device 0 are also called MII registers.

**MDIO** and **MMD** Register Interface Description

### 4.2 Register Naming and Numbering

The register numbering convention in this document is similar to that of IEEE 802.3:

The numbering syntax uses 3 numbers "a.b.c" as specified in IEEE 802.3 paragraph 45.1, and the notation is generalized to Clause 22 registers in device 0 "STD". The alphanumeric syntax also uses the same structure and uses the names of the MMD devices, registers and register fields separated by underscore and dot as described below.

### 4.2.1 Register Numbering

The syntax is as follows, with a, b, c written as decimal numbers:

a.b.c = <DEVICE\_NUMBER>.<REGISTER\_NUMBER>.<FIELD\_NUMBER>

When the last indicator (c) is omitted, the register numbering refers to the full register.

When a field is more than a single bit, the bit range is indicated using a semicolon (e.g. 1:3 is the field of bits 1 to 3). In an MDIO register, the least significant bit is bit 0 and most significant bit is bit 15. All MDIO registers are 16 bit wide.

### 4.2.2 Register Naming

The syntax is as follows, with AA, BB, CC written as alphanumeric strings:

AA.BB.CC = <DEVICE\_NAME>\_<REGISTER\_NAME>.<FIELD\_NAME>

When the last indicator (CC) is omitted, the register naming refers to the full register.

The fields named RES, refer to reserved fields as per IEEE 802.3 documents.

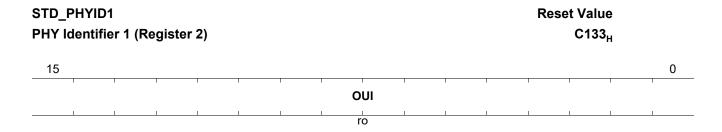

#### 4.2.3 Examples

STD\_STAT.ANOK is the name of the field 0.1.5, which indicates auto-negotiation complete.

ANEG\_CTRL.ANEG\_RESTART is the name of the field 7.0.9, which allows the STA to restart the Ethernet ANEG procedure.

34

ANEG\_PHYID1 is the complete 16-bit register number 7.2, for the PHY identifier 1 number.

**MDIO** and **MMD** Register Interface Description

#### 4.3 MMD Devices Present in MxL86110

Table 13 lists the devices present in the MxL86110.

Table 13 MMD Devices Present in MxL86110

| MDIO / MMD Name | Device Number (decimal) | Description                                                           |

|-----------------|-------------------------|-----------------------------------------------------------------------|

| PCS             | 3                       | Control and status registers related to PCS encoding/decoding device. |

| ANEG            | 7                       | Control and status registers related to auto-negotiation device.      |

### 4.4 Responsibilities of the STA

The MMD devices implement groups of standardized registers under the management of the STA. They are defined in IEEE 802.3.

As per IEEE 802.3 guidelines, it is the responsibility of the STA entity to ensure that mutually acceptable speeds are applied consistently across all the MMDs of the MxL86110.

#### 4.5 MDIO Access Protocols to Read / Write Registers

All the MDIO/MMD registers can be accessed from an external chip connected to the MDIO bus on the MDIO and MDC pins. The MxL86110 supports several MDIO frame protocols:

- · Clause 22: To access Device 0

- Clause 22 Extended: To access other devices (Dev 3: PCS, Dev 7: ANEG,) using the indirection scheme specified by IEEE 802.3.

- Clause 45: to access device as Table 13.

Both Clause 22 Extended and Clause 45 can be used to access MMD devices. However, the mechanism implemented in the MxL86110 provides faster speeds using Clause 45, so there are some differences in latencies in the MDIO reply:

- Protocol "Clause 22 Extended" involves the MxL86110 an indirection mechanism.

- Protocol "Clause 45" provides faster replies.

The Clause 22 registers can be accessed using the Clause 45 electrical interface and the Clause 22 management frame structure (IEEE 802.3 section 45.2).

**MDIO Registers Detailed Description**

## 5 MDIO Registers Detailed Description

Table 14 MDIO Register Access Type

| Mode                                                                                             | Symbol |

|--------------------------------------------------------------------------------------------------|--------|

| Status Register (Status, or Ability Register)                                                    | RO     |

| Read-Write Register (e.g. MDIO Register)                                                         | RW     |

| Read-Write, Self-Clearing Register. The bit is cleared after being read from the MDIO interface. | RWSC   |

Attention: Since the MxL86110 is a 1000 Mbit/s product, the maximum speed capability availabe in the registers is 1000 Mbit/s. Any speed higher than 1000 Mbit/s, such as 2.5 Gbit/s, 5 Gbit/s, or 10 Gbit/s, defaults to 1000 Mbit/s.

## 5.1 Standard Management Registers

This section describes the IEEE 802.3 standard management registers corresponding to Clause 22.

Table 15 Registers Overview - Standard Management

| Register Short Name | Register Long Name                                                     | Reset Value                     |

|---------------------|------------------------------------------------------------------------|---------------------------------|

| STD_CTRL            | STD Control (Register 0)                                               | 1140 <sub>H</sub>               |

| STD_STAT            | Status Register (Register 1)                                           | 7949 <sub>H</sub>               |

| STD_PHYID1          | PHY Identifier 1 (Register 2)                                          | C133 <sub>H</sub>               |

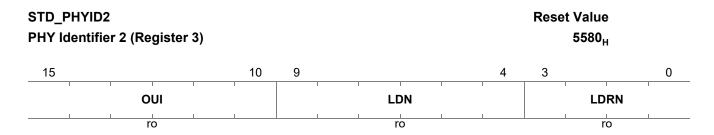

| STD_PHYID2          | PHY Identifier 2 (Register 3)                                          | 5580 <sub>H</sub> <sup>1)</sup> |

| STD_AN_ADV          | Auto-Negotiation Advertisement (Register 4)                            | 11E1 <sub>H</sub>               |

| STD_AN_LPA          | Auto-Negotiation Link Partner Ability (Register 5)                     | 0000 <sub>H</sub>               |

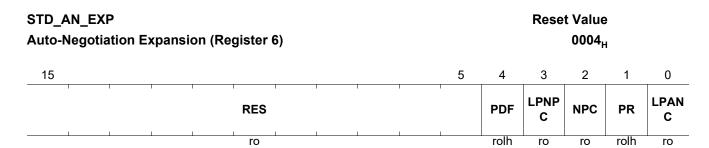

| STD_AN_EXP          | Auto-Negotiation Expansion (Register 6)                                | 0004 <sub>H</sub>               |

| STD_AN_NPTX         | Auto-Negotiation Next Page Transmit Register (Register 7)              | 2001 <sub>H</sub>               |

| STD_AN_NPRX         | Auto-Negotiation Link Partner Received Next Page Register (Register 8) | 0000 <sub>H</sub>               |

| STD_GCTRL           | Gigabit Control Register (Register 9)                                  | 0200 <sub>H</sub>               |

| STD_GSTAT           | Gigabit Status Register (Register 10)                                  | 0000 <sub>H</sub>               |

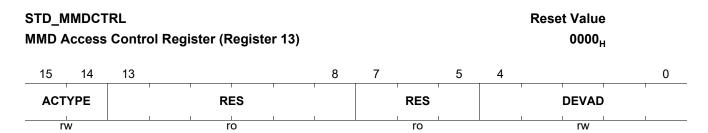

| STD_MMDCTRL         | MMD Access Control Register (Register 13)                              | 0000 <sub>H</sub>               |

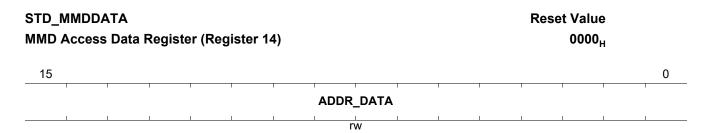

| STD_MMDDATA         | MMD Access Data Register (Register 14)                                 | 0000 <sub>H</sub>               |

| STD_XSTAT           | Extended Status Register (Register 15)                                 | 2000 <sub>H</sub>               |

<sup>1)</sup> For the device specific reset value, refer to the Product Naming table in the **Package Outline** chapter.

## 5.1.1 Standard Management Registers

This chapter describes all registers of STD in detail.

## STD Control (Register 0)

This register controls the main functions of the PHY.

IEEE Standard Register=0

STD\_CTRL **Reset Value** STD Control (Register 0) 1140<sub>H</sub> 15 14 13 12 11 10 9 8 7 6 5 0 RST LB SSL ANEN PD ISOL ANRS DPLX COL SSM RES rwsc ro rw rw rw rw rwsc rw rw rw

| Field | Bits | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST   | 15   | RWSC | Reset Resets the PHY to its default state. Active links are terminated. Note that this is a self-clearing bit which is set to zero by the hardware after reset has been done.  0 <sub>B</sub> NORMAL Normal operational mode 1 <sub>B</sub> RESET Resets the device                                                                                                                                                                                                                                                                                                                  |

| LB    | 14   | RW   | Loopback on GMII This mode enables looping back of MII data from the transmit to the receive direction. No data is transmitted to the Ethernet PHY. The device operates at the selected speed. The collision signal remains de-asserted unless otherwise forced by the collision test.  O <sub>B</sub> NORMAL Normal operational mode  1 <sub>B</sub> ENABLE Closes the loopback from Tx to Rx at xMII                                                                                                                                                                               |

| SSL   | 13   | RW   | Forced Speed Selection LSB This bit only takes effect with the auto-negotiation process is disabled (STD_CTRL.ANEN bit is set to 0 <sub>B</sub> ). This is the lower bit (LSB) of the forced speed selection. In conjunction with the higher bit (MSB), this encoding is valid: The standard procedure to force 2500 Mbit/s operation (when ANEG is disabled) is to program PMA_CTRL with 1.0.6 = 1.0.13 = 1 and 1.0.5:2 = [0 1 1 0 ] PHY mirrors 1.0.6, 1.0.13 and 0.0.6, 0.0.13 MSB LSB bit values: 00 <sub>B</sub> 10 Mbit/s 01 <sub>B</sub> 1000 Mbit/s 11 <sub>B</sub> Reserved |

| Field | Bits | Type | Description (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                          |