# XR77103-MoCA Universal PMIC 3 Output Buck Regulator

**EVB User Manual**

# **Revision History**

| Document No. | Release Date      | Change Description |

|--------------|-------------------|--------------------|

| 010-MCUMR00  | February 14, 2022 | Initial release.   |

## **Table of Contents**

| Introduction                   | 1  |

|--------------------------------|----|

| Quick EVB Set Up and Start Up  | 1  |

| Factory Settings               | 1  |

| Quick Start Up                 | 1  |

| Reference Documentation        | 3  |

| Ordering Information           | 3  |

| Evaluation Board Overview      | 4  |

| I/O and Test Points            |    |

| System Set-Up                  | 5  |

| Jumper J3                      | 5  |

| Jumper J8                      | 5  |

| Jumper J11                     | 5  |

| XR77103-MoCA Schematic         |    |

| XR77103-MoCA PCB Layers        | 8  |

| XR77103-MoCA Bill of Materials | 10 |

# List of Figures

| Figure 1: Connecting and Monitoring V <sub>IN</sub> and V <sub>OUT</sub> | 2 |

|--------------------------------------------------------------------------|---|

| Figure 2: Top View of XR77103-MoCA                                       |   |

| Figure 3: Simplified Block Diagram, XR77103-MoCA                         |   |

| Figure 4: XR77103-MoCA Schematic                                         |   |

| Figure 5: Silkscreen Top                                                 | 8 |

| Figure 6: Assembly Top/Layer 1                                           | 8 |

| Figure 7: Layer 2                                                        | 8 |

| Figure 8: Layer 3                                                        | 8 |

| Figure 9: Assembly Bottom                                                | 9 |

## **List of Tables**

| Table 1: Jumper Connections for V <sub>IN</sub> , V <sub>OUT</sub> and PGND | 1  |

|-----------------------------------------------------------------------------|----|

| Table 2: Evaluation Board Ordering Part Number                              | 3  |

| Table 3: Test Points                                                        |    |

| Table 4: Factory Settings                                                   | 5  |

| Table 5: Jumper J3 Options for the EN Pin                                   | 5  |

| Table 6: Jumper J8 Pull Up Options for the PGOOD Pin                        | 5  |

| Table 7: Jumper J11 and Operation from a 5V Rail                            | 6  |

| Table 8: XR77103MoCA Bill of Materials                                      | 10 |

#### Introduction

The XR77103-MoCA PMIC is designed to power MaxLinear's MoCA 2.0 MxL370x and MoCA 2.5 MxL371x along with a single port Ethernet PHY such as the GPY241 device. It features three high efficiency synchronous buck regulators with integrated power switches and sequencing engine to provide the 0.9V, 1.8V, and 3.3V rails of the MoCA SoC. The 0.9V core rail can supply the 3A peaks demanded by the SoC and is compatible with the SoC DVS control.

The XR77103-MoCA can operate with 5V, 9V, and 12V powered systems with minimal required external components. The XR77103-MoCA is also packaged in a 4x4mm QGN which provides the smallest size solution possible.

### Quick EVB Set Up and Start Up

#### **Factory Settings**

The evaluation board has been set up with the following factory default configuration for guick set up and operation:

- V<sub>IN</sub> = 5.5V to 14V, optimized for a 12V input rail.

- Maximum I<sub>OUT</sub> per channel is 2A.

- Hz Switching frequency.

- Two channels may be paralleled for output currents up to 5A peak and 4A steady state (however additional hardware modification is required for parallel operation).

- Low power spectral density (PSM) mode operation enabled.

#### Quick Start Up

To quickly see the regulator in operation:

- Use the factory settings and default configuration. If other settings or components are desired, apply them before the next steps. For more information, see "System Set-Up" on page 5 for more.

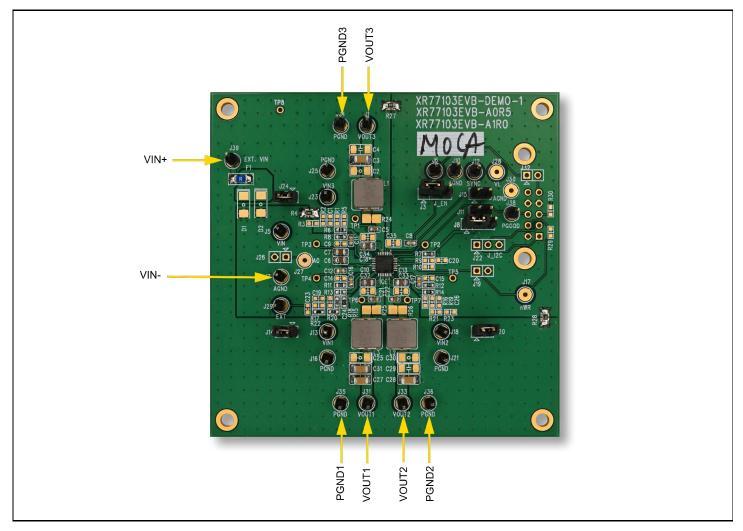

- 2. Connect a turned-off power supply that is within the above V<sub>IN</sub> specification (from 5.5V to 14V, 12V typical) to V<sub>IN</sub>+ and V<sub>IN</sub>- with short and thick leads. Use test pins EXT. VIN (J39) and AGND (J7) to connect and monitor V<sub>IN</sub>+ and V<sub>IN</sub>- respectively. See locations in Figure 1 on page 2.

- 3. Initially set to 0A, connect electronic loads to each desired channel that will be no more than the maximum I<sub>OUT</sub> (2A) to VOUTx and PGNDx (where x = the channel number) with short and thick leads. Use test pins in Table 1 on page 1 to connect and monitor VOUTx and PGNDx respectively. See locations in Figure 1 on page 2. For all channels with the electronic load connected, ensure that the respective V<sub>IN</sub> jumper is installed per Table 1 on page 1.

- 4. Turn on the 12V power supply and check V<sub>OUT</sub>. The EVB powers up and regulates the enabled outputs at 0.9V (Ch1), 1.8V (Ch2) and 3.3V (Ch3) (factory default settings). PGOOD is asserted active high once sequencing is done, outputs are in regulation, and reset timer expires.

- 5. Set or vary the load (do not exceed the maximum I<sub>OUT</sub>) and check V<sub>OUT</sub> and other desired performance levels such as regulation and efficiency. For more information about monitoring, see "I/O and Test Points" on page 4.

Table 1: Jumper Connections for V<sub>IN</sub>, V<sub>OUT</sub> and PGND

| Channel | V <sub>IN</sub> <sup>(1)</sup> | V <sub>OUT</sub> | PGND       |

|---------|--------------------------------|------------------|------------|

| 1       | J14                            | VOUT1, J31       | PGND1, J35 |

| 2       | J20                            | VOUT2, J33       | PGND2, J36 |

| 3       | J24                            | VOUT3, J1        | PGND3, J4  |

1. Factory default: jumpers installed.

Figure 1: Connecting and Monitoring  $V_{\text{IN}}$  and  $V_{\text{OUT}}$

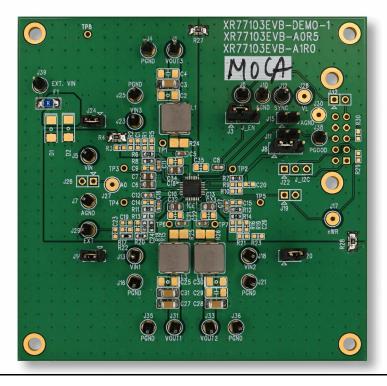

Figure 2: Top View of XR77103-MoCA

#### Reference Documentation

For additional information, refer to the XR77103-MoCA data sheet, including a full list of IC features, pinout, pin descriptions, typical performance characteristics, and external component calculations.

This manual provides the EVB schematics ("XR77103-MoCA Schematic" on page 7), the PCB layout ("XR77103-MoCA Schematic" on page 7) and the bill of materials ("XR77103-MoCA Bill of Materials" on page 10) that you can use on your board design.

For more information about the schematics, go to www.maxlinear.com/XR77103-MoCA.

## **Ordering Information**

**Table 2: Evaluation Board Ordering Part Number**

| <b>Evaluation Board</b> | Board Description              |

|-------------------------|--------------------------------|

| XR77103-MoCA-EVK-1      | XR77103-MoCA evaluation board. |

Note: For the most up-to-date information, go to www.maxlinear.com/XR77103-MoCA.

#### **Evaluation Board Overview**

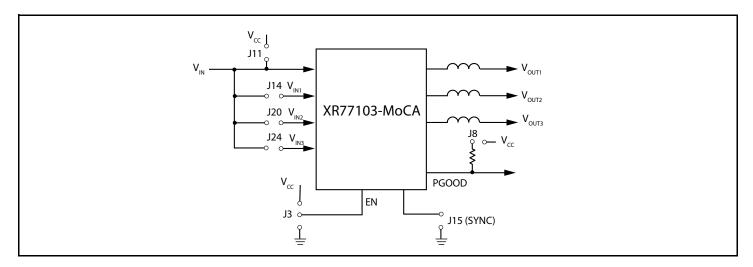

The XR77103-MoCA block diagram is shown in Figure 3.

Figure 3: Simplified Block Diagram, XR77103-MoCA

#### I/O and Test Points

## VIN, LX and PGOOD Test Points

Test points are available for VIN (TP8), the LX switching nodes (TP6 for LX1, TP7 for LX2, and TP1 for LX3), the compensation pins (TP4 for COMP1, TP5 for COMP2, TP3 for COMP3), and PGOOD (TP2) for monitoring.

**Table 3: Test Points**

| Test Point | Function |

|------------|----------|

| TP1        | LX3      |

| TP2        | PGOOD    |

| TP3        | COMP3    |

| TP4        | COMP1    |

| TP5        | COMP2    |

| TP6        | LX1      |

| TP7        | LX7      |

| TP8        | VIN      |

The PGOOD output can be used externally. For more information about PGOOD options, see "Jumper J8" on page 5.

## System Set-Up

Table 4 lists a summary of the jumpers and factory settings to configure the EVB for operation. For additional information, refer to the XR77103-MoCA data sheet (206DS).

**Table 4: Factory Settings**

| Jumper                | Factory Setting   | Description                                                                           |  |  |  |

|-----------------------|-------------------|---------------------------------------------------------------------------------------|--|--|--|

| EN Pin                |                   |                                                                                       |  |  |  |

| J3                    | Jumper 1-2        | EN pin is tied to $V_{\mbox{\footnotesize CC}}$ and channels are enabled at power up. |  |  |  |

| PGOOD Pin             | +                 |                                                                                       |  |  |  |

| J8                    | Jumper 1-2        | PGOOD is pulled up to V <sub>CC</sub> .                                               |  |  |  |

| 5V Operation          |                   |                                                                                       |  |  |  |

| J11                   | No jumper         | LDO output is not tied to V <sub>IN</sub> .                                           |  |  |  |

| VIN Connection to Ind | ividual Channels  |                                                                                       |  |  |  |

| J14, J20, J24         | Jumpers installed | VIN is connected to VIN1, VIN2, and VIN3.                                             |  |  |  |

| SYNC Pin              |                   |                                                                                       |  |  |  |

| J15                   | No jumper         | SYNC is not tied to GND on the board.                                                 |  |  |  |

## Jumper J3

#### Table 5: Jumper J3 Options for the EN Pin

| Jumper Options       | Description                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------|

| Jumper 1-2 (default) | The EN (enable) pin is tied to $V_{\mbox{\footnotesize CC}}$ and channels are enabled at power up. |

| Jumper 2-3           | The EN (enable) pin is tied to GND, permanently disabling the channels.                            |

| No jumper            | The jumper is open, allowing EN to be controlled external to the board.                            |

## Jumper J8

#### Table 6: Jumper J8 Pull Up Options for the PGOOD Pin

| Jumper Options       | Description                            |

|----------------------|----------------------------------------|

| Jumper 1-2 (default) | PGOOD is pulled up to the VCC pin.     |

| No jumper            | PGOOD is not pulled up by this jumper. |

#### Jumper J11

For operation from a 5V rail, it is required that the LDO output is connected to  $V_{IN}$ , which can be accomplished by populating J11. This enhances the operation of the drivers for  $V_{IN}$  < 5V.

**Important:** Remove J11 for operation at higher  $V_{IN}$ . The board also has Zener diode placeholders which can be installed to protect the IC if higher  $V_{IN}$  is accidentally applied.

Table 7: Jumper J11 and Operation from a 5V Rail

| Jumper Options      | Description                                                                |

|---------------------|----------------------------------------------------------------------------|

| Jumper 1-2          | Ties the LDO output to $V_{\text{IN}}$ which is required for 5V operation. |

| No jumper (default) | LDO output is not tied to V <sub>IN</sub> .                                |

## Jumpers J14, J20 and J24

Jumpers J14, J20 and J24 are available to connect or disconnect VIN from VIN1, VIN2, and VIN3 respectively. Factory default is VIN is connected to VIN1, VIN2, and VIN3.

## Jumper J15

Jumper J15 is available to ground SYNC. Factory default is that the SYNC pin is grounded on the board. When not grounded, the SYNC pin may be connected and synchronized to an external clock in applications where EMI control is critical.

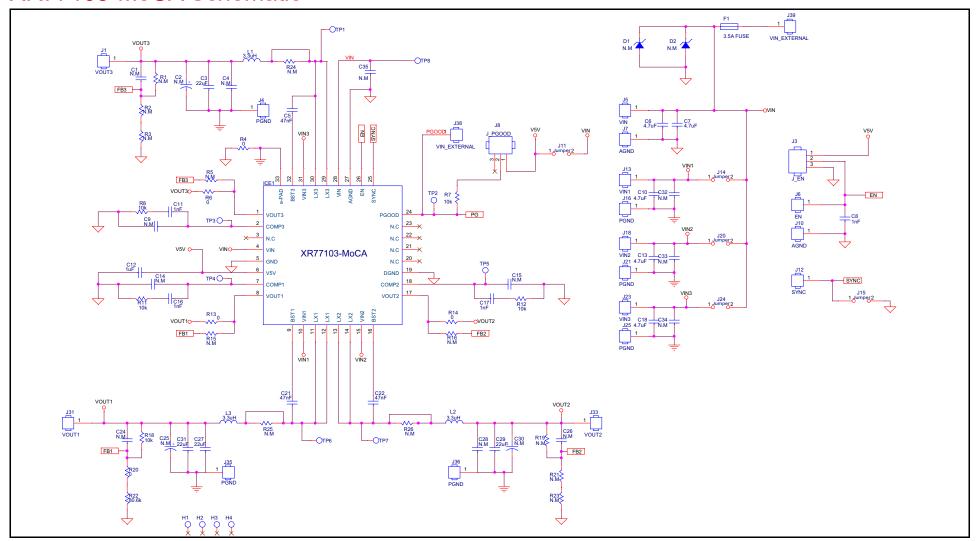

## XR77103-MoCA Schematic

Figure 4: XR77103-MoCA Schematic

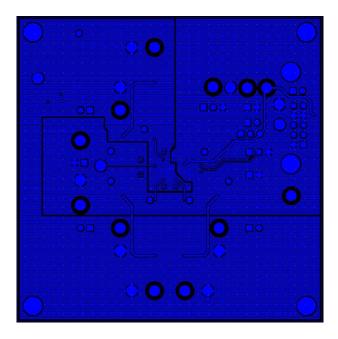

## XR77103-MoCA PCB Layers

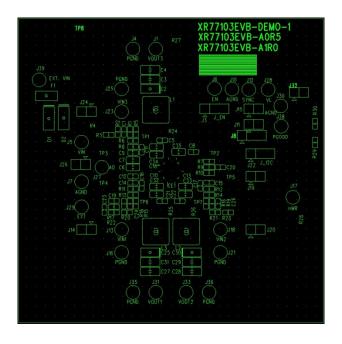

Figure 5: Silkscreen Top

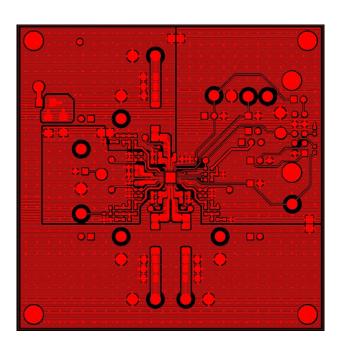

Figure 6: Assembly Top/Layer 1

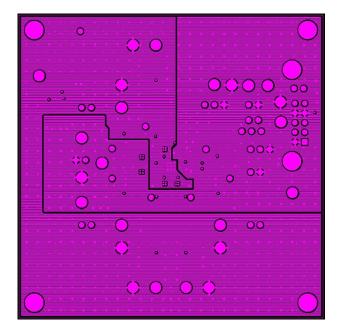

Figure 7: Layer 2

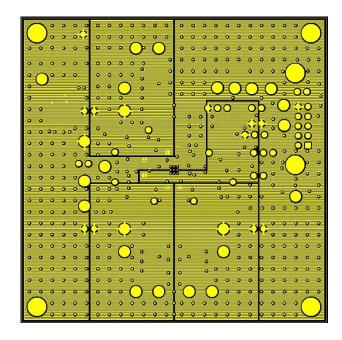

Figure 8: Layer 3

Figure 9: Assembly Bottom

## XR77103-MoCA Bill of Materials

#### Table 8: XR77103MoCA Bill of Materials

| Item | Qty | Reference Designator                                                                          | Component                              | Manufacturer /<br>Part Number   | Package<br>Size  |

|------|-----|-----------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|------------------|

| 1    | 1   | PCB                                                                                           | XR77103 Evaluation Board               | MaxLinear                       |                  |

| 2    | 4   | C3, C27, C29, C31                                                                             | CAP CER 22uF 16V X5R 1206 10%          | Murata<br>GRM31CR61C226KE15K    | 1206             |

| 3    | 3   | C5, C21, C22                                                                                  | CAP CER 47nF 50V X7R 10%               | Murata<br>GRM188R71H473KA61D    | 0603             |

| 4    | 5   | C6, C7, C10, C13, C18                                                                         | CAP CER 4.7uF 25V X7R 10%              | Murata<br>GRM21BR71E475KA73L    | 0805             |

| 5    | 4   | C8, C11, C16, C17                                                                             | CAP CER 1nF 50V X7R 10%                | Murata<br>GRM188R71H102KA01D    | 0603             |

| 6    | 1   | C12                                                                                           | CAP CER 1uF, 10V, X7R, 10%             | Murata<br>GRM188R71A105KA61D    | 0603             |

| 7    | 7   | R4,R6,R13,R14,R20,R27,R28                                                                     | Resistor 0Ω,1/10W, SMD                 | Panasonic<br>ERJ-3GEY0R00V      | 0603             |

| 8    | 5   | R7,R8,R11R12,R18                                                                              | Resistor 10.0kΩ, 1/10W, 1%, SMD        | Panasonic<br>ERJ-3EFK1002V      | 0603             |

| 9    | 1   | R22                                                                                           | Resistor 80.6kΩ, 1/10W, 1%, SMD        | Panasonic<br>ERJ-3EFK80603V     |                  |

| 10   | 1   | F1                                                                                            | Fuse Board Mount 3.5A, 63VDC           | Vishay<br>MFU1206FF03500P100    | 1206             |

| 11   | 20  | J1, J4, J5, J6, J7, J10, J12, J13, J16, J18, J21, J23, J25, J29, J31, J33, J35, J36, J38, J39 | Header 1-pin                           | Wurth Elektronik<br>61300111121 | 2.54mm           |

| 12   | 2   | J3, J8                                                                                        | Header 3-pin                           | Wurth Elektronik<br>61300311121 | 2.54mm           |

| 13   | 5   | J11, J14, J15, J20, J24                                                                       | Jumper 2-pin                           | Wurth Elektronik<br>61300211121 | 2.54mm           |

| 14   | 3   | L1, L2, L3                                                                                    | Inductor 3.3μH, 6A, 30mΩ, SMD          | Vishay<br>IHLP2525CZER3R3M01    | 6.86 x<br>6.47mm |

| 15   | 1   | U1                                                                                            | Universal PMIC 3 Output Buck Regulator | MaxLinear<br>XR77103ELBTR-MoCA  | 4mm x 4mm        |

Corporate Headquarters: 5966 La Place Court, Suite 100 Carlsbad, CA 92008

Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598

www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. \*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2022 MaxLinear, Inc. All rights reserved.