### **GSW120**

**Ethernet Switch**

# 4-Port Gigabit Ethernet Switch with 2 Integrated Gigabit Ethernet PHYs

GSW120 (GSW120A3MC) GSW120 (GSW120A3LC)

### **Data Sheet**

Revision 1.8, 2023-01-19 Reference ID 617931

#### Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

MaxLinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

\*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2023 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008

Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

#### **Revision History**

| Current:<br>Previous:                      | Revision 1.8, 2023-01-19<br>Revision 1.7, 2022-03-15                      |  |  |  |  |

|--------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Page Major changes since previous revision |                                                                           |  |  |  |  |

| 1                                          | Updated the Cover Page.                                                   |  |  |  |  |

| 13                                         | Updated Section 1.1, Features.                                            |  |  |  |  |

| 20                                         | Updated Section 1.3, Block Diagram.                                       |  |  |  |  |

| 25                                         | Jpdated Table 5, Ethernet Media Independent Interface Signals.            |  |  |  |  |

| 27                                         | Updated Table 6, LED Interface Signals.                                   |  |  |  |  |

| 32                                         | Updated Table 9, Power Supply Pins.                                       |  |  |  |  |

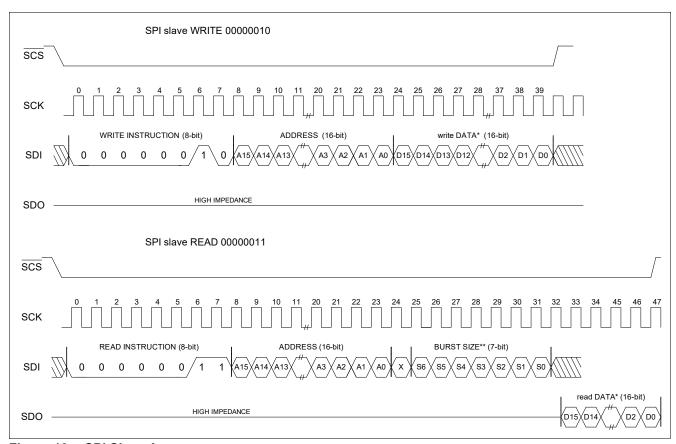

| 42                                         | Updated Section 3.2.5, SPI Slave Access.                                  |  |  |  |  |

| 68                                         | Added Section 3.6.3, RMII Configuration.                                  |  |  |  |  |

| 138                                        | Updated xMII Interface 5 Configuration Register.                          |  |  |  |  |

| 215                                        | Removed external PHY interrupts from IM0 Interrupt Status Register.       |  |  |  |  |

| 215                                        | Removed external PHY interrupts from IM0 EINT0 Interrupt Enable Register. |  |  |  |  |

| 216                                        | Removed external PHY interrupts from IM0 EINT1 Interrupt Enable Register. |  |  |  |  |

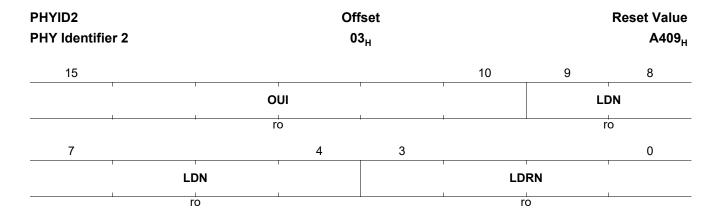

| 274                                        | Updated PHYID2 reset value in Table 60, Registers Overview.               |  |  |  |  |

| 274                                        | Updated reset value in the PHY Identifier 2 register.                     |  |  |  |  |

| 334                                        | Added Section 5.5.7, RMII Interface Timing Characteristics.               |  |  |  |  |

#### **Table of Contents**

|         | Table of Contents                                 | . 4 |

|---------|---------------------------------------------------|-----|

|         | List of Figures                                   | . 8 |

|         | List of Tables                                    | 10  |

| 1       | Product Overview                                  | 12  |

| 1.1     | Features                                          | 13  |

| 1.2     | Applications                                      | 17  |

| 1.3     | Block Diagram                                     | 20  |

| 2       | External Signals                                  | 21  |

| 2.1     | Logic Symbol                                      | 21  |

| 2.2     | External Signal Description                       | 22  |

| 2.2.1   | Pin Diagram                                       |     |

| 2.2.2   | Abbreviations                                     |     |

| 2.2.3   | Input/Output Signals                              | 24  |

| 2.2.3.1 | Ethernet Media Interface                          |     |

| 2.2.3.2 | SGMII Interface                                   |     |

| 2.2.3.3 | Ethernet Media Independent Interface              |     |

| 2.2.3.4 | LED/UART/JTAG Interface                           |     |

| 2.2.3.5 | Management Interfaces                             |     |

| 2.2.3.6 | Miscellaneous Signals                             |     |

| 2.2.3.7 | Power Supply                                      | 32  |

| 3       | Functional Description                            | 33  |

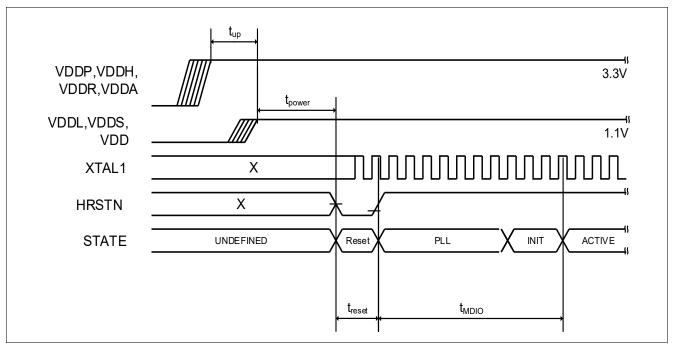

| 3.1     | Clock and Reset                                   | 33  |

| 3.1.1   | Clock Generation Unit                             | 33  |

| 3.1.2   | General Purpose Clock Output                      | 33  |

| 3.1.3   | Reset Generation Unit                             | 33  |

| 3.1.4   | Power Up Sequence                                 | 33  |

| 3.2     | Management Interface Functional Description       |     |

| 3.2.1   | Management Interface Subsystem Features           |     |

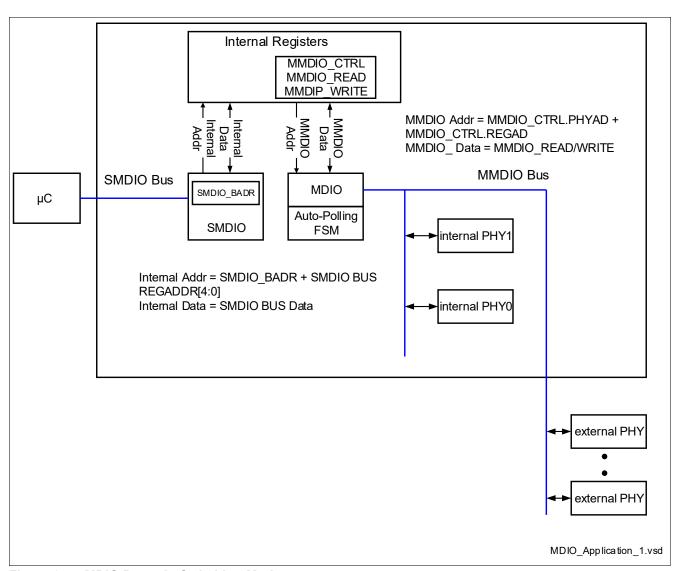

| 3.2.2   | MDIO Master Module                                |     |

| 3.2.3   | MDIO Slave Module                                 |     |

| 3.2.4   | SPI Master Module                                 |     |

| 3.2.5   | SPI Slave Access                                  |     |

| 3.2.6   | UART Access                                       |     |

| 3.2.7   | Boot Loader Description                           |     |

| 3.2.8   | Packet Insertion and Extraction                   |     |

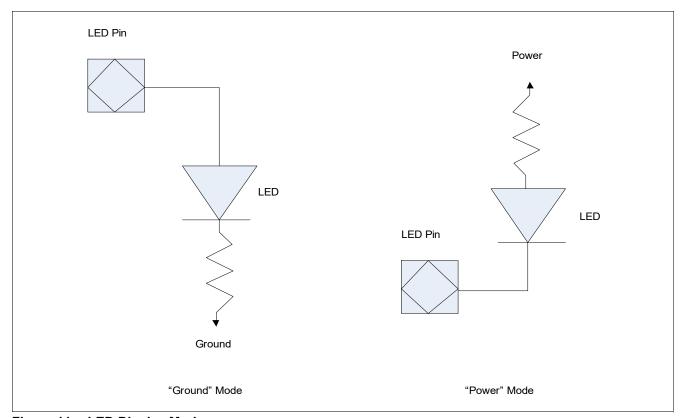

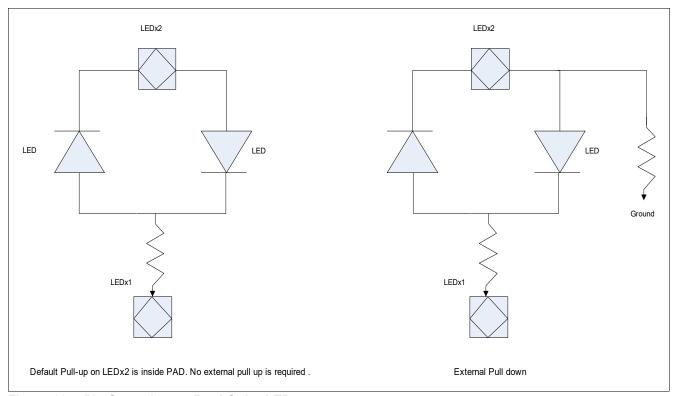

| 3.3     | LED Controller Function Description               |     |

| 3.3.1   | LED                                               |     |

| 3.3.2   | LED Display                                       |     |

| 3.3.3   | LED Brightness Control                            |     |

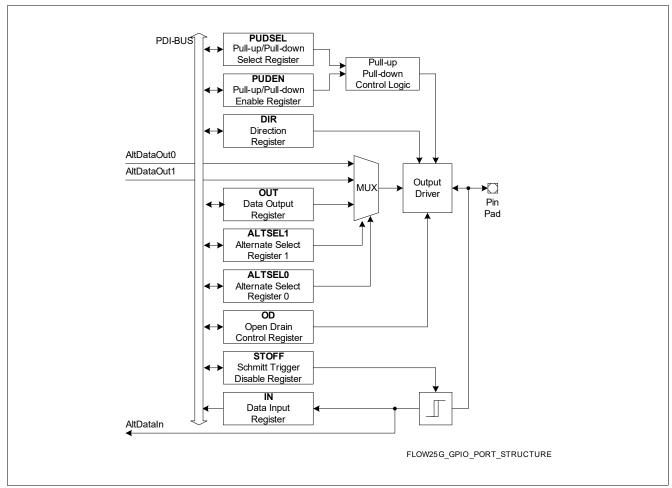

| 3.4     | General Purpose Input Output Function Description |     |

| 3.5     | Gigabit Ethernet PHY Functional Description       |     |

| 3.5.1   | Features                                          |     |

| 3.5.2   | Functional Description                            |     |

| 3.5.2.1 | Twisted-Pair Interface                            |     |

| 3.5.2.2 | Auto-Negotiation (ANEG)                           |     |

| 3.5.2.3 | Auto-Downspeed                                    |     |

| 3.5.2.4 | Auto-Crossover and Polarity-Reversal Correction   | co  |

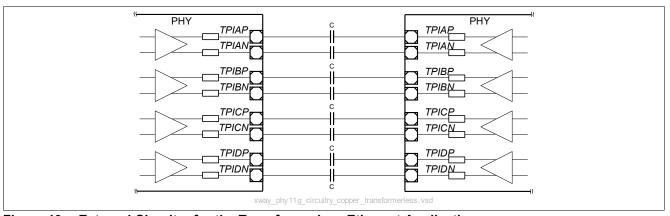

| 3.5.2.5   | Transformerless Ethernet (TLE)                   | 65 |

|-----------|--------------------------------------------------|----|

| 3.5.2.6   | Configuration and Control via MDIO               | 66 |

| 3.5.2.7   | Power Management                                 | 66 |

| 3.5.2.7.1 | Power Down Modes                                 | 66 |

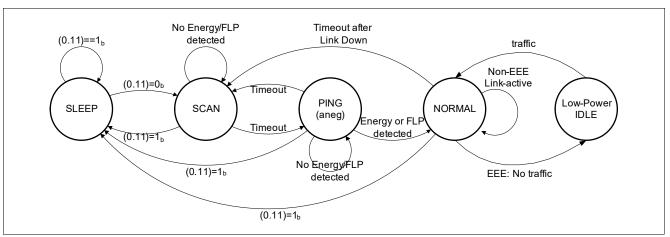

| 3.5.2.7.2 | Sleep Mode                                       | 66 |

| 3.5.2.7.3 | Scan Mode                                        | 66 |

| 3.5.2.7.4 | Ping Mode                                        | 66 |

| 3.5.2.7.5 | Normal Mode                                      |    |

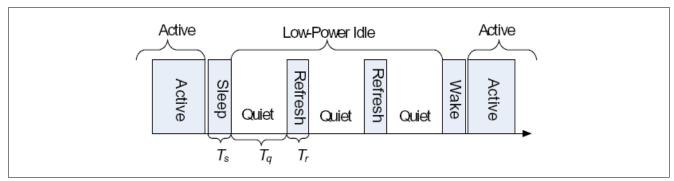

| 3.5.2.7.6 | Low-Power Idle Mode: Energy-Efficient Ethernet   |    |

| 3.6       | Reduced Media-Independent Interface              |    |

| 3.6.1     | Features                                         |    |

| 3.6.2     | Functional Description                           |    |

| 3.6.3     | RMII Configuration                               |    |

|           | SGMII Interface Function Description             |    |

| 3.7.1     | Features                                         |    |

| 3.7.2     | Functional Description                           |    |

| 3.7.2.1   | Typical Applications                             | 69 |

| 3.7.2.1.1 | Interface to an External MAC                     |    |

| 3.7.2.1.2 | Interface to an External 1000BASE-T Ethernet PHY | 69 |

| 3.7.2.1.3 | Interface to an External 1000BASE-X Ethernet PHY | 70 |

| 3.7.2.2   | Modes of Operation                               | 70 |

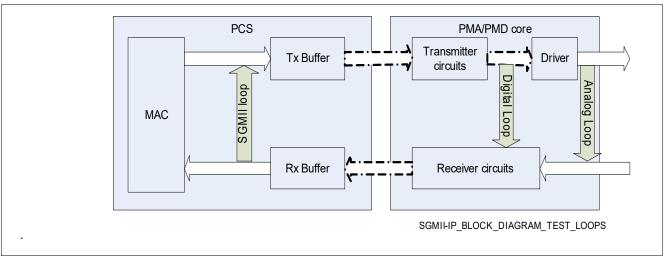

| 3.7.2.3   | Test Features, Status and Enabling               | 71 |

| 3.7.2.3.1 | PMA/PMD Loops                                    | 71 |

| 3.7.2.3.2 | PCS Loops                                        | 71 |

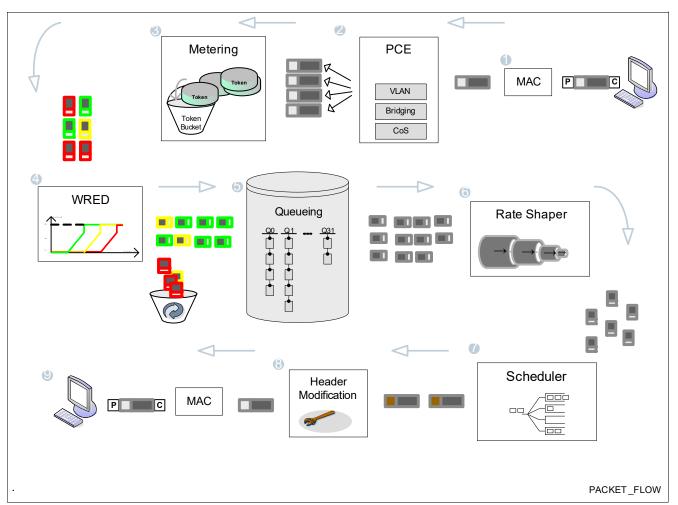

| 3.8       | Switch Fabric Functional Description             | 72 |

| 3.8.1     | Overview                                         |    |

| 3.8.2     | Ethernet Bridging                                | 73 |

| 3.8.2.1   | Parsing                                          | 73 |

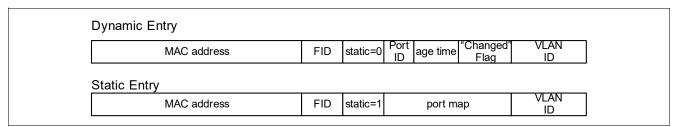

| 3.8.2.2   | MAC Bridging Table                               |    |

| 3.8.2.3   | MAC Based Forwarding                             |    |

| 3.8.2.4   | Dynamic Source MAC Address Learning and Aging    | 74 |

| 3.8.2.5   | Layer 2 Security                                 | 76 |

| 3.8.2.6   | Spanning Tree Protocol Support                   | 78 |

| 3.8.2.7   | Reserved MAC Addresses                           | 78 |

| 3.8.2.8   | Flow Control Function                            | 79 |

| 3.8.2.9   | Port Trunking Functions                          |    |

| 3.8.2.10  | Gigabit Media Access Control (GMAC) Functions    |    |

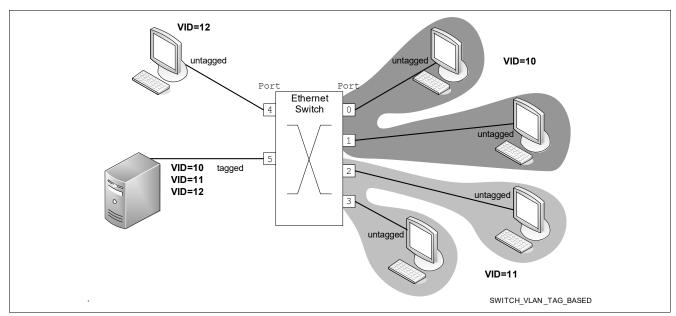

| 3.8.3     | VLAN Functions                                   | 82 |

| 3.8.3.1   | VLAN Association                                 | 82 |

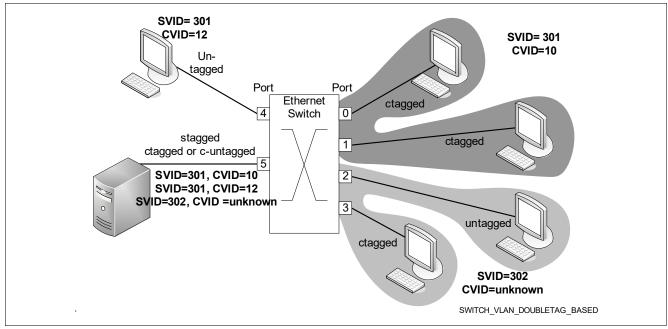

| 3.8.3.2   | VLAN QinQ                                        |    |

| 3.8.3.3   | Supported Frame Format                           | 83 |

| 3.8.3.4   | Double VLAN Tag Function                         |    |

| 3.8.3.5   | Filtering Identifier Assignment                  |    |

| 3.8.3.6   | VLAN Filtering                                   |    |

| 3.8.3.7   | VLAN Tagging and Untagging                       | 85 |

| 3.8.3.8   | Transparent VLAN Mode                            |    |

| 3.8.3.9   | VLAN Security Mode                               |    |

| 3.8.3.10  | Reserved VLAN Groups                             |    |

| 3.8.3.11  | VLAN Translation                                 |    |

| 3.8.3.12  | VLAN Priority Code Point                         |    |

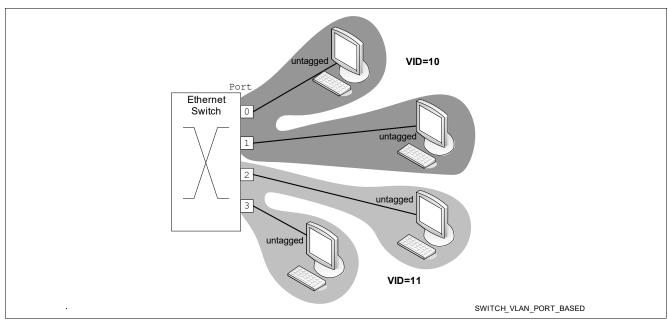

| 3.8.3.13  | Port Based VLAN Examples                         | 88 |

| 3.8.3.14                   | Single Tag Based VLAN Examples                         |  |

|----------------------------|--------------------------------------------------------|--|

| 3.8.3.15                   | Double Tag Based VLAN Examples                         |  |

| 3.8.4                      | Multicast Forwarding Functions                         |  |

| 3.8.4.1                    | Layer-2 Multicast Forwarding                           |  |

| 3.8.4.2                    | Layer-3 Multicast Forwarding                           |  |

| 3.8.4.3                    | IGMP and MLD Snooping                                  |  |

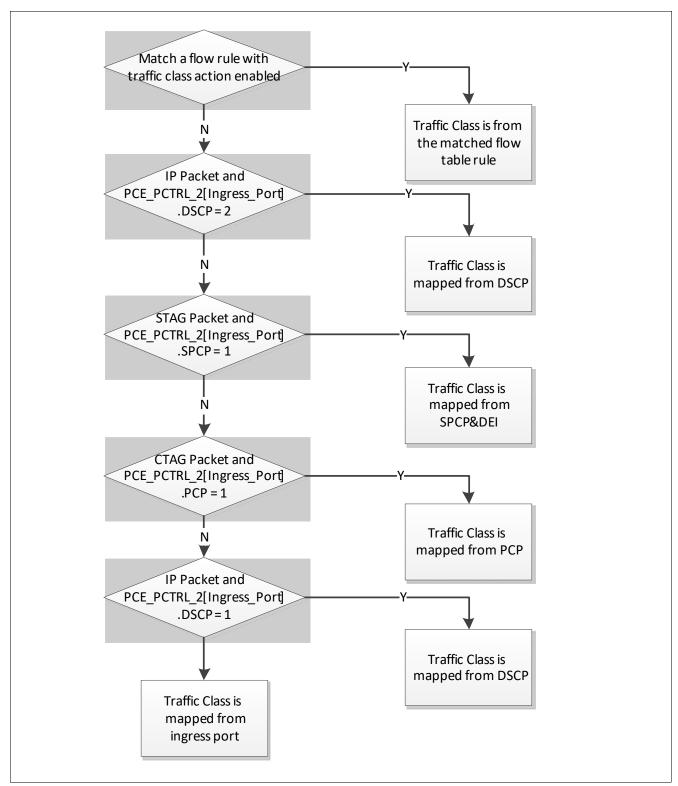

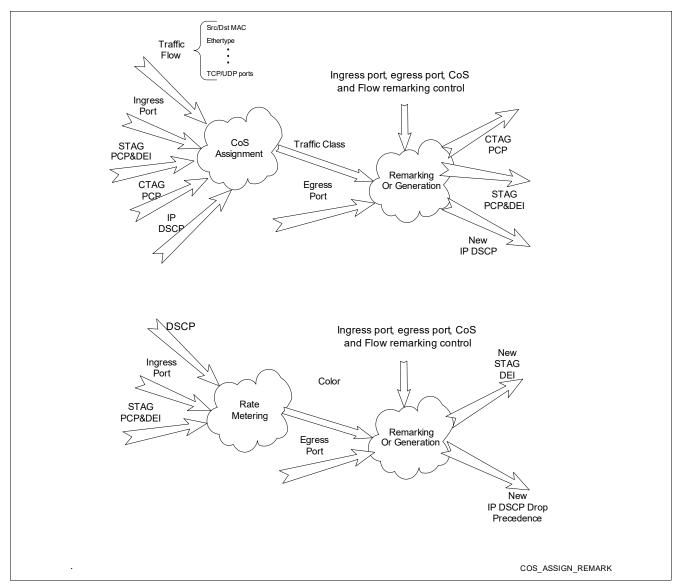

| 3.8.5                      | Quality of Service Functions                           |  |

| 3.8.5.1                    | Class of Service Assignment                            |  |

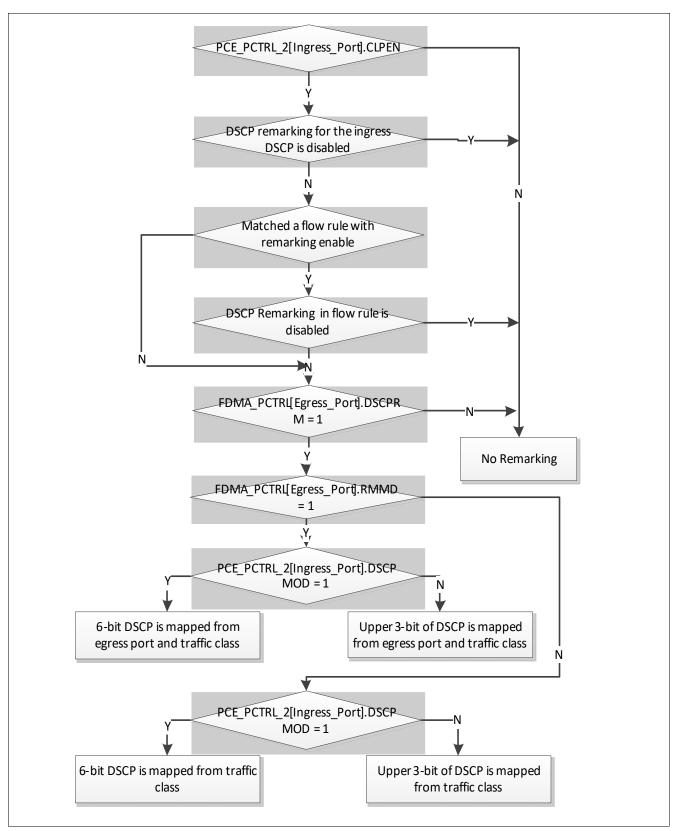

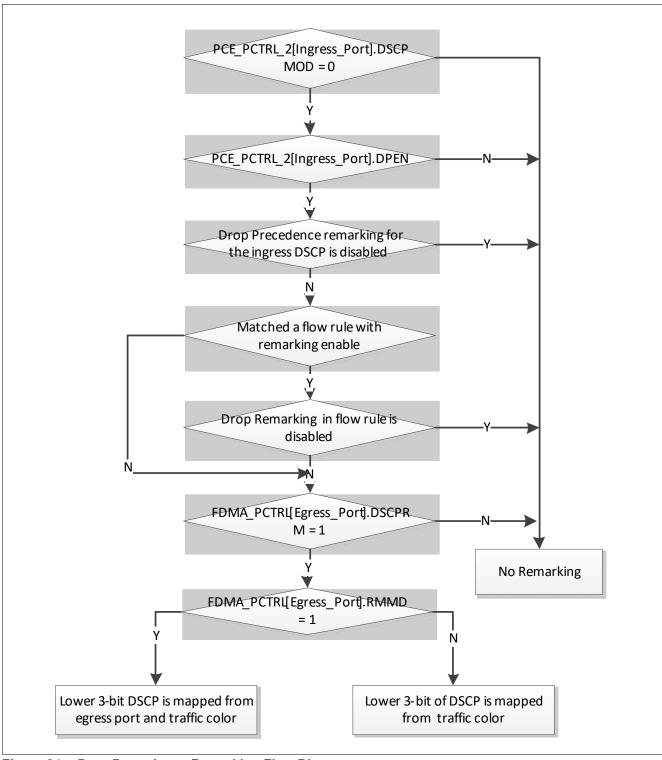

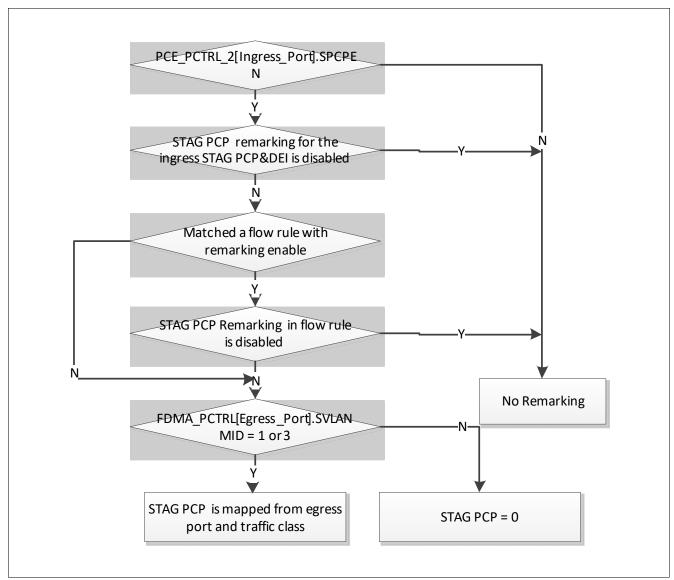

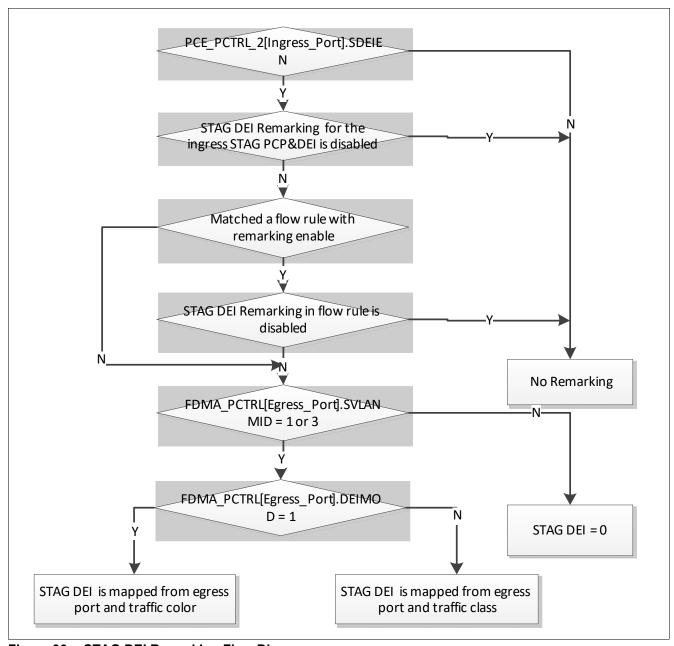

| 3.8.5.2                    | Remarking Function                                     |  |

| 3.8.5.3                    | Queue Mapping                                          |  |

| 3.8.5.4                    | Rate Metering                                          |  |

| 3.8.5.5<br>3.8.5.6         | , •                                                    |  |

| 3.8.5.7                    | Queue Scheduling                                       |  |

| 3.8.5.8                    | Congestion Management                                  |  |

|                            | Ingress Port Congestion Based Flow Control             |  |

| 3.8.5.9<br>3.8.5.10        | Storm Control                                          |  |

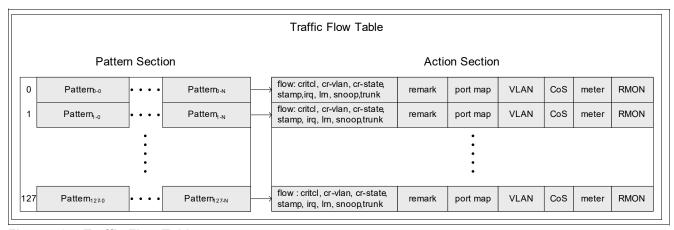

| 3.8.6                      | Flow Classification Function                           |  |

| 3.8.7                      | Operation, Administration, and Management Functions    |  |

| 3.8.7.1                    | Monitoring Counters                                    |  |

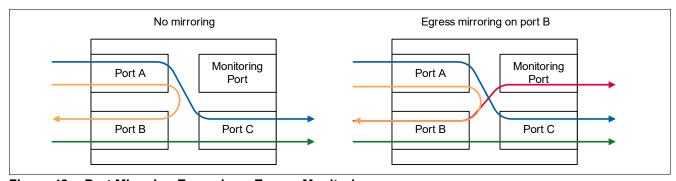

| 3.8.7.1                    | Port Mirroring                                         |  |

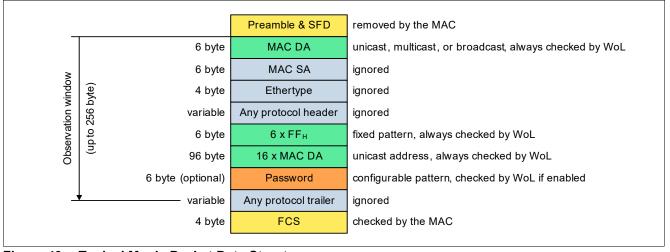

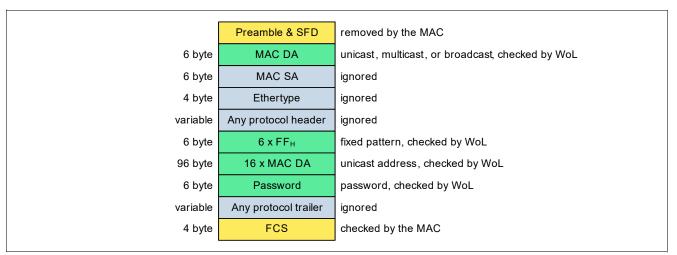

| 3.8.7.3                    | Wake-on-LAN Functionality                              |  |

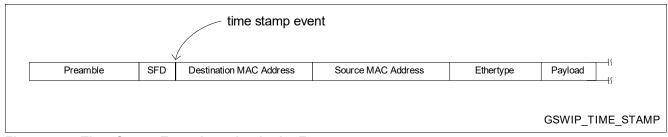

| 3.8.7.4                    | Time Stamp Functionality                               |  |

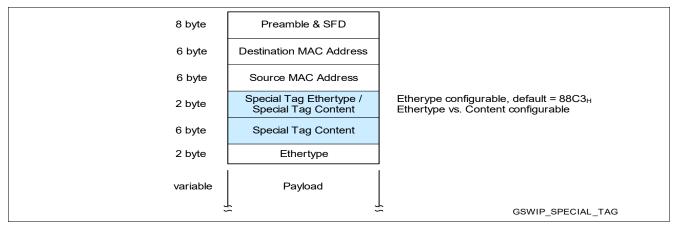

| 3.8.7.5                    | Special Tag Functionality                              |  |

|                            |                                                        |  |

| 4                          | Registers                                              |  |

| 4.1<br>4.1.1               | Top Level PDI Registers                                |  |

| 4.1.1<br>4.1.2             | GPHY Shell Registers                                   |  |

| 4.1.2<br>4.1.3             | R(G)MII Registers                                      |  |

| 4.1.3<br>4.1.4             | MDIO Slave Registers                                   |  |

| 4.1. <del>4</del><br>4.1.5 | SPI Master Registers                                   |  |

| 4.1.5<br>4.1.6             | SPI Slave Registers                                    |  |

| 4.1.7                      | UART Registers                                         |  |

| 4.1.7                      | · · · · · · · · · · · · · · · · · · ·                  |  |

| 4.1.9                      | Clock Generation Unit Registers                        |  |

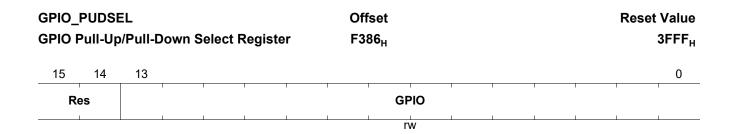

| 4.1.10                     | GPIO Registers                                         |  |

| 4.1.10                     | ICU Registers                                          |  |

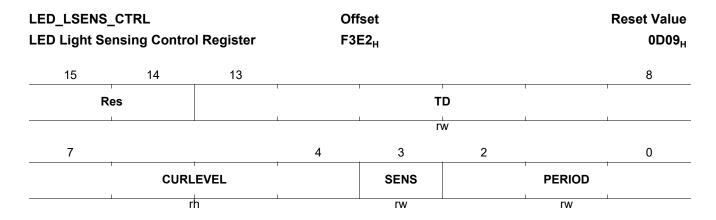

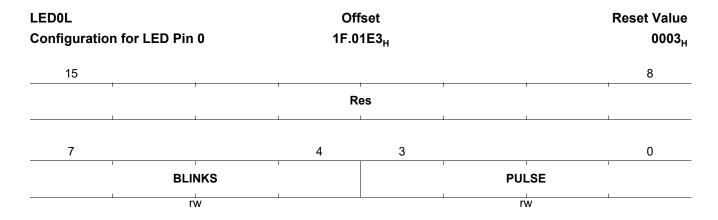

| 4.1.11                     | LED Registers                                          |  |

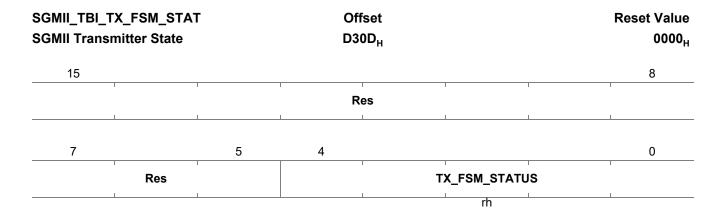

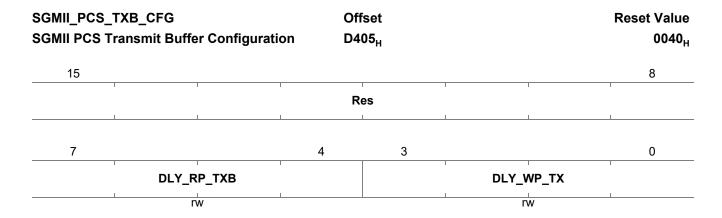

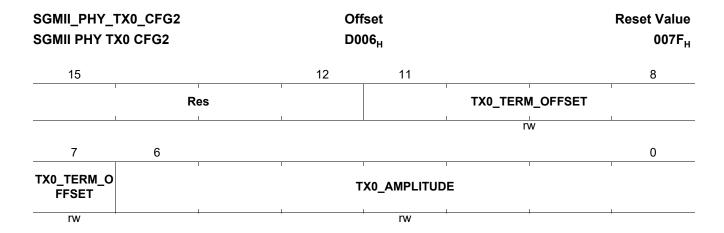

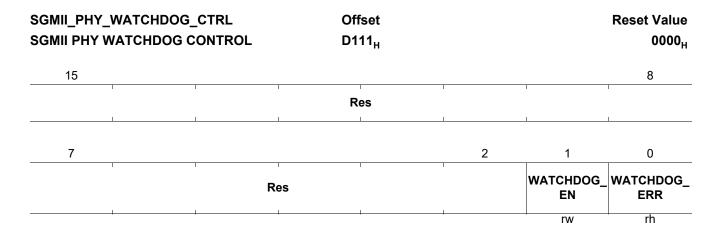

| 4.1.12                     | SGMII_Registers                                        |  |

| 4.2.1                      | SGMII_TBI: TBI Submodule Register File                 |  |

| 4.2.2                      | SGMII_PCS: SGMII PCS Register File                     |  |

| 4.2.3                      | SGMII PHY: SGMII PHY Registers                         |  |

| 4.2.4                      | SGMII_MACRO_REGISTERS: SGMII_MACRO Registers           |  |

| 4.3                        | PHY MDIO Registers                                     |  |

| 4.3.1                      | STD: Standard Management Registers                     |  |

| 4.3.2                      | PHY: PHY-Specific Management Registers                 |  |

| 4.3.2<br>4.4               | PHY MMD Registers                                      |  |

| 4.4.1                      | PMAPMD: Standard PMAPMD Registers for MMD=0x01         |  |

| 4.4.2                      | EEE: Standard EEE Registers for MMD=0x03               |  |

| 4.4.3                      | ANEG: Standard Auto-Negotiation Registers for MMD=0x07 |  |

| 4.4.4                      | INTERNAL: Internal Address Space (MMD=0x1F)            |  |

|                            | ······································                 |  |

| 5         | Electrical Characteristics                   | 325 |

|-----------|----------------------------------------------|-----|

| 5.1       | Absolute Maximum Ratings                     | 325 |

| 5.2       | Operating Range                              | 326 |

| 5.3       | Power Consumption                            | 327 |

| 5.4       | DC Characteristics                           | 328 |

| 5.4.1     | Digital Interfaces                           | 328 |

| 5.4.1.1   | GPIO Interfaces                              | 328 |

| 5.4.1.2   | RGMII Transmit Interface                     | 328 |

| 5.4.1.3   | RGMII Receive Interface                      | 329 |

| 5.5       | AC Characteristics                           | 330 |

| 5.5.1     | Reset                                        | 330 |

| 5.5.2     | Power Supply                                 | 331 |

| 5.5.3     | Input Clock                                  | 331 |

| 5.5.4     | Output Clock                                 | 331 |

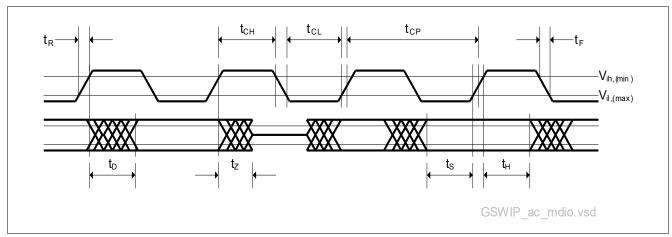

| 5.5.5     | MDIO Interface                               | 332 |

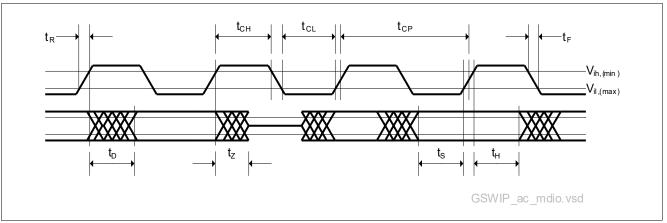

| 5.5.6     | SMDIO Interface                              | 333 |

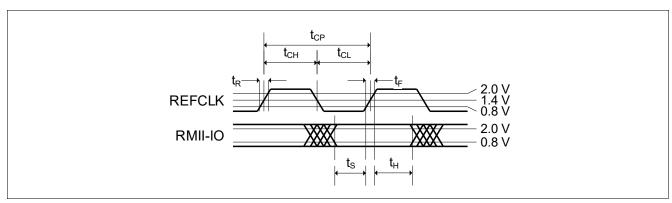

| 5.5.7     | RMII Interface Timing Characteristics        | 334 |

| 5.5.8     | RGMII Interface Timing Characteristics       | 335 |

| 5.5.8.1   | RGMII Interface                              | 335 |

| 5.5.8.2   | SGMII Interface                              | 336 |

| 5.5.8.2.1 | Transmit Timing Characteristics              | 336 |

| 5.5.8.2.2 | Receive Timing Characteristics               | 337 |

| 5.5.9     | Test Interface                               | 338 |

| 5.5.10    | Crystal Specification                        | 339 |

| 5.5.11    | Transformers (Magnetics)                     | 339 |

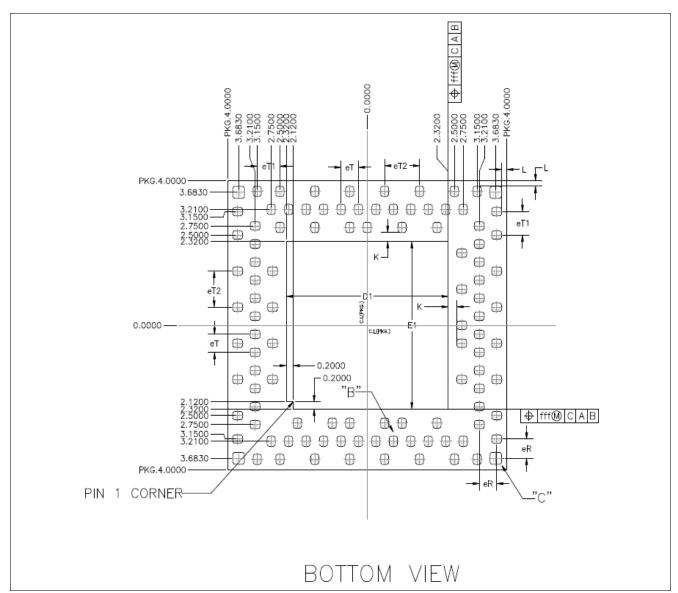

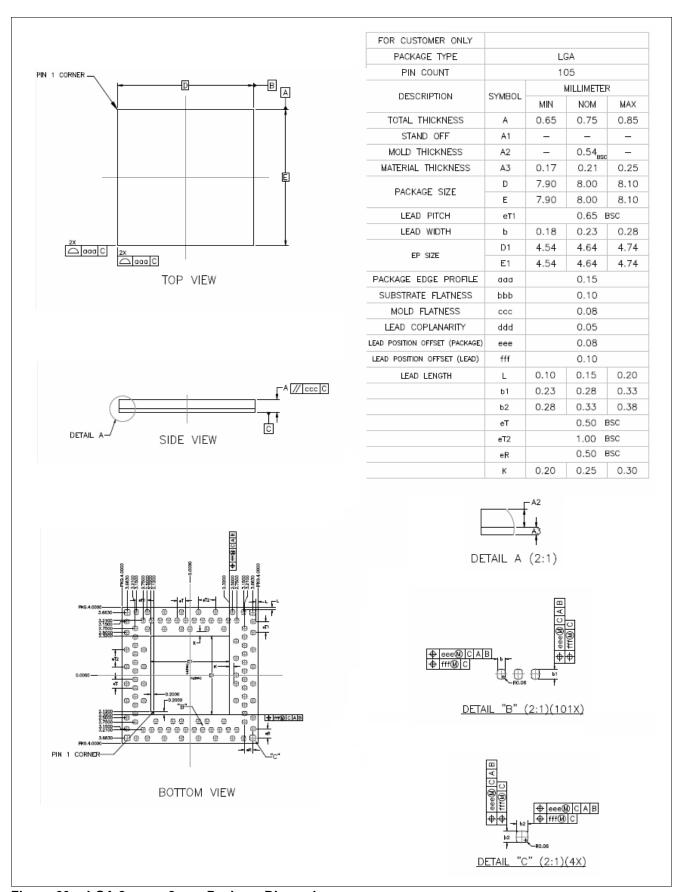

| 6         | Package Outline                              | 341 |

| 6.1       | PG-MRQFN-105 Package                         |     |

| 6.2       | LGA-105 Package                              |     |

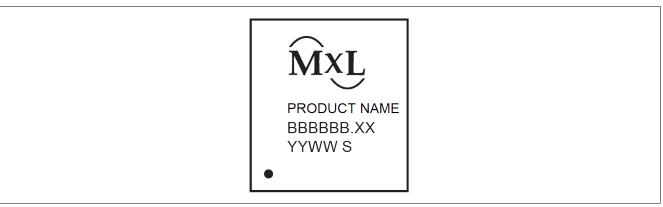

| 6.3       | Chip Identification and Ordering Information |     |

|           | Standards References                         | 346 |

#### **List of Figures**

### **List of Figures**

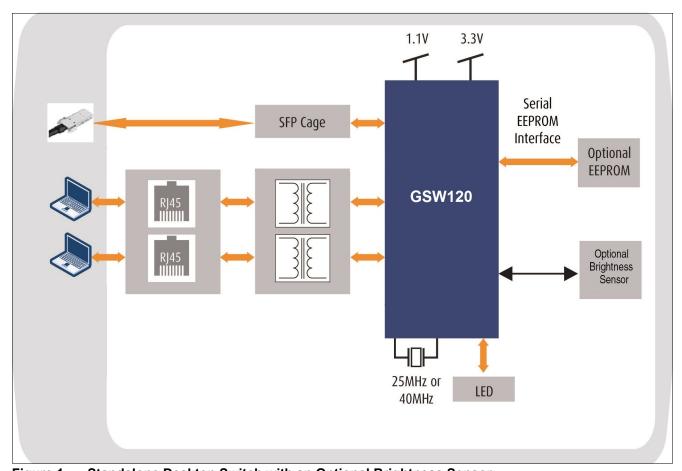

| Figure 1  | Standalone Desktop Switch with an Optional Brightness Sensor          | 17    |

|-----------|-----------------------------------------------------------------------|-------|

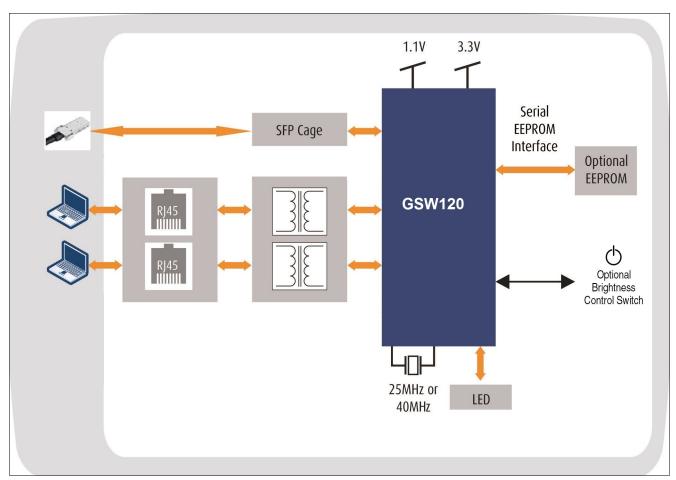

| Figure 2  | Standalone Desktop Switch with an Optional Brightness Control Switch  | 18    |

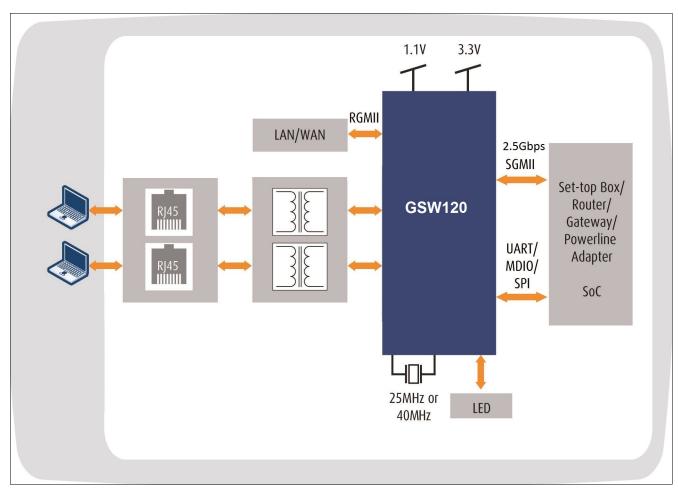

| Figure 3  | Home Gateway                                                          | 19    |

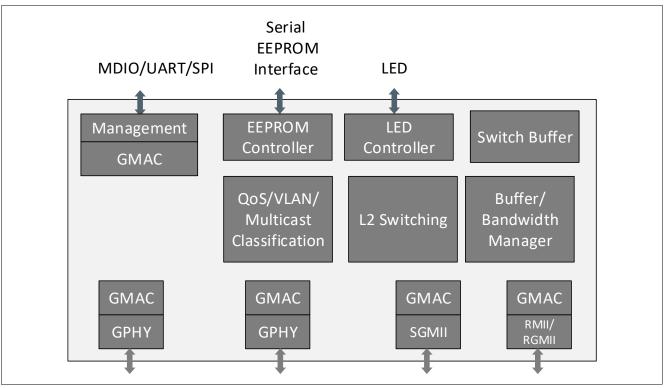

| Figure 4  | Block Diagram                                                         | 20    |

| Figure 5  | GSW120 Logic Symbol                                                   | 21    |

| Figure 6  | Pin Layout.                                                           | 22    |

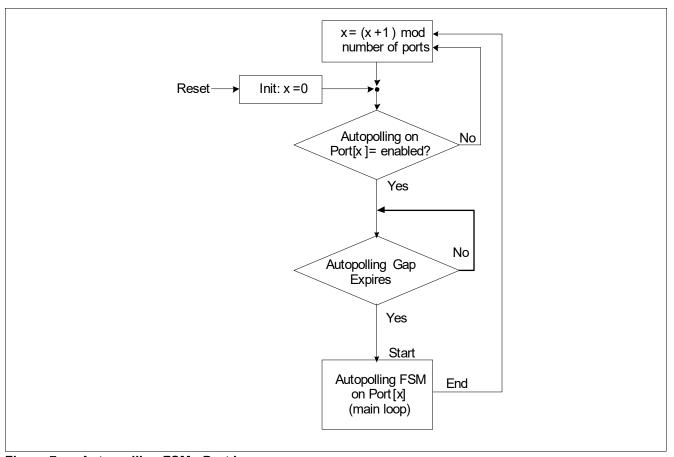

| Figure 7  | Auto-polling FSM - Port Loop                                          | 36    |

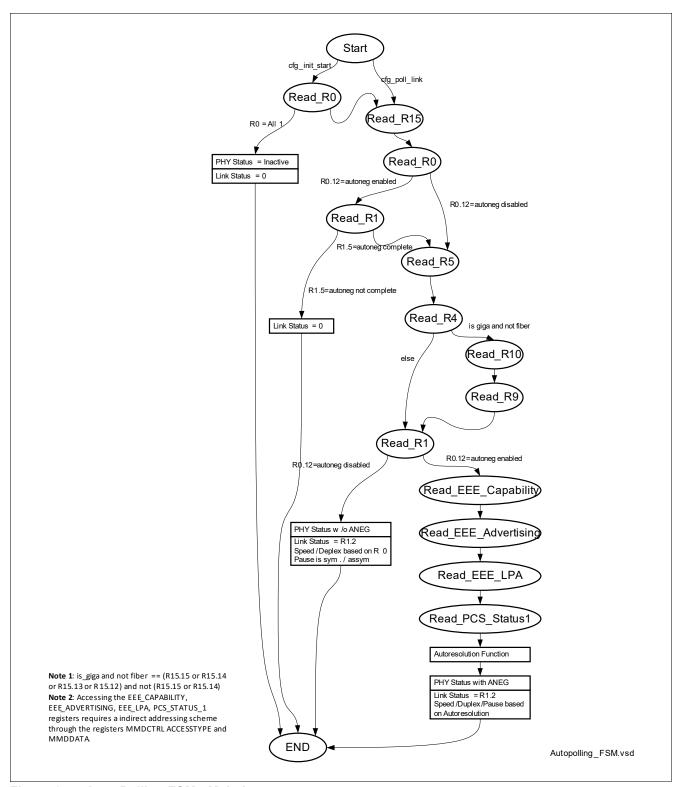

| Figure 8  | Auto Polling FSM - Main Loop                                          | 37    |

| Figure 9  | MDIO Proxy in Switching Mode                                          | 39    |

| Figure 10 | SPI Slave Access                                                      | 42    |

| Figure 11 | LED Display Mode                                                      | 57    |

| Figure 12 | Pin Strapping on Dual Color LED                                       | 58    |

| Figure 13 | Pin Strapping on Single Color LED                                     | 58    |

| Figure 14 | LED Brightness Control By Controlling LED Output Enable/Disable       | 59    |

| Figure 15 | Direct 2 Level LED Control Enable on System Board (with Pull-Up)      | 60    |

| Figure 16 | Light Sensing System                                                  | 61    |

| Figure 17 | General Port Structure                                                | 62    |

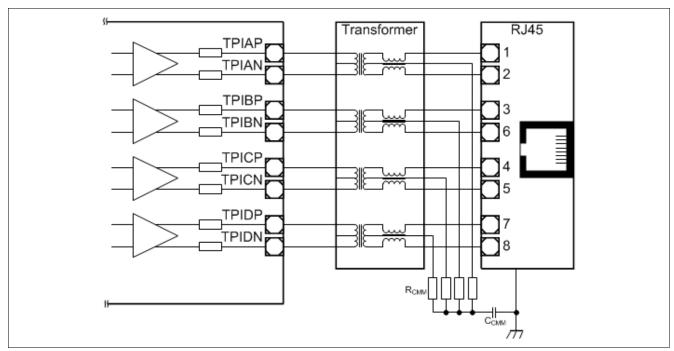

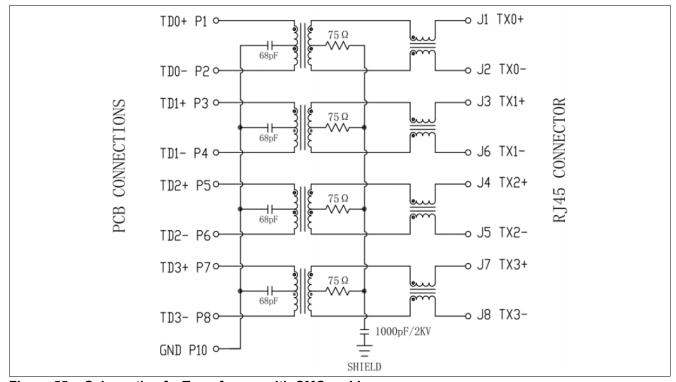

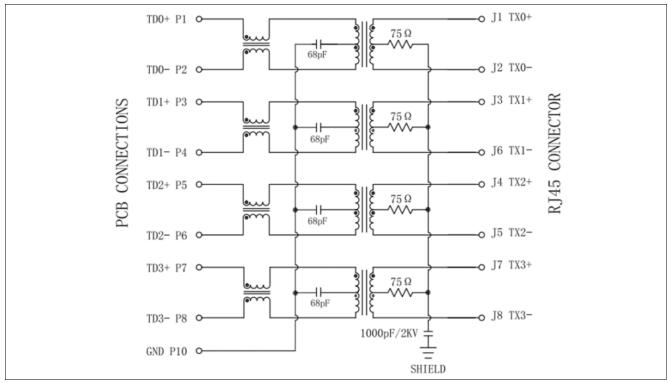

| Figure 18 | Twisted-Pair Interface of GPHY IP Including Transformer and RJ45 Plug | 64    |

| Figure 19 | External Circuitry for the Transformerless Ethernet Application       |       |

| Figure 20 | State Diagram for Power-Down Mode Management                          | 66    |

| Figure 21 | EEE Low-Power Idle Sequence                                           |       |

| Figure 22 | Test Loops in the GSW120                                              |       |

| Figure 23 | Packet Flow Diagram                                                   | 72    |

| Figure 24 | MAC Bridge Table Entry Formats                                        |       |

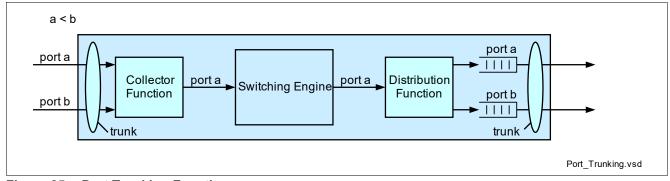

| Figure 25 | Port Trunking Function                                                |       |

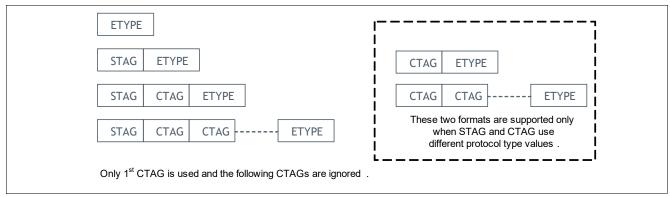

| Figure 26 | Supported Frame Formats when STAG is enabled                          |       |

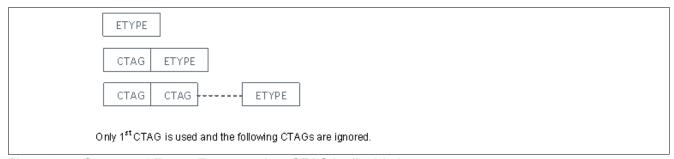

| Figure 27 | Supported Frame Formats when STAG is disabled                         |       |

| Figure 28 | Port-based VLAN Example                                               |       |

| Figure 29 | Tag-based VLAN Example                                                |       |

| Figure 30 | Double Tag and Port based VLAN Example                                |       |

| Figure 31 | Traffic Class Assignment                                              |       |

| Figure 32 | PCP/DSCP /DEI Remarking                                               |       |

| Figure 33 | DSCP Remarking Flow Diagram                                           |       |

| Figure 34 | Drop Precedence Remarking Flow Diagram                                |       |

| Figure 35 | STAG PCP Remarking Flow Diagram                                       |       |

| Figure 36 | STAG DEI Remarking Flow Diagram                                       |       |

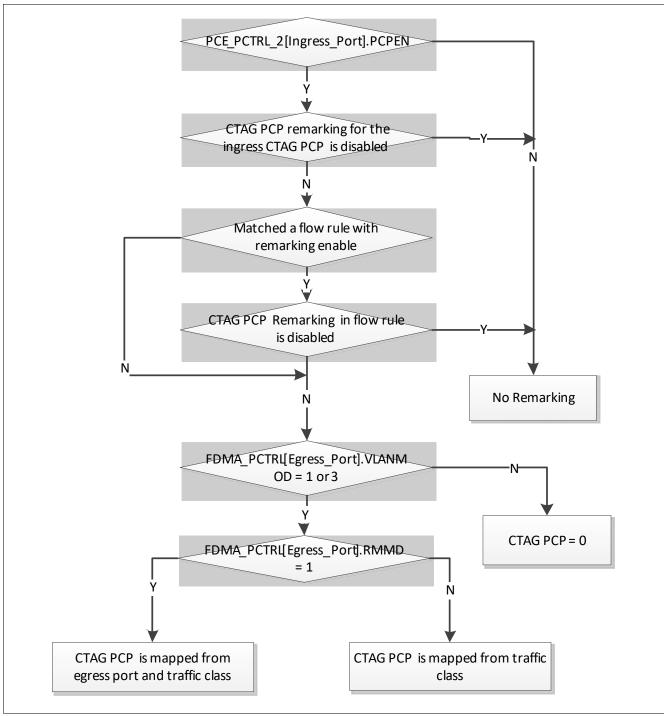

| Figure 37 | CTAG PCP Remarking Flow Diagram                                       |       |

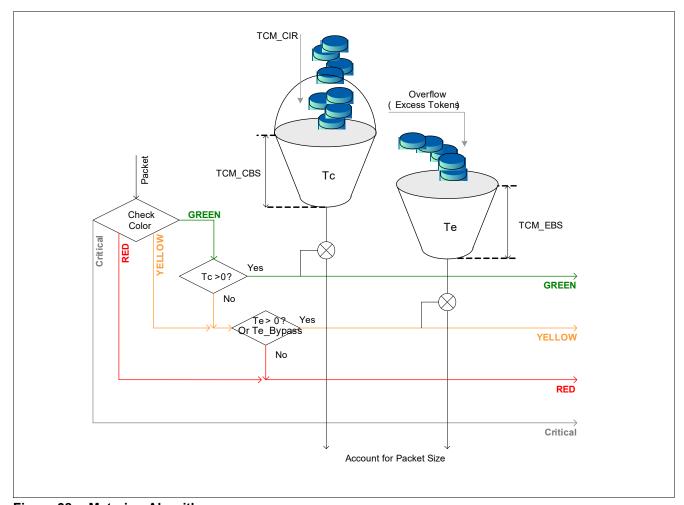

| Figure 38 | Metering Algorithm                                                    |       |

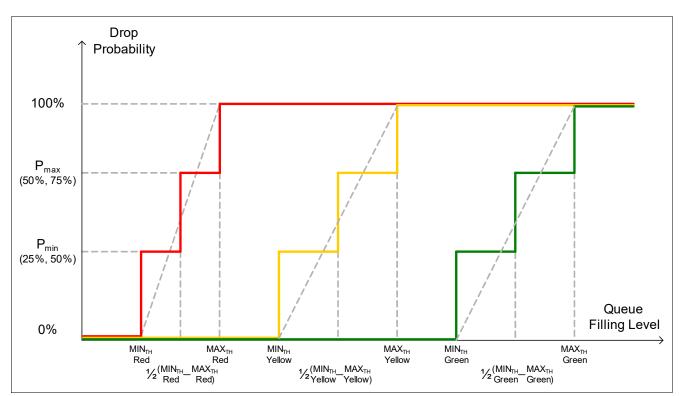

| Figure 39 | Drop Precedence Thresholds                                            |       |

| Figure 40 | Traffic Flow Table                                                    |       |

| Figure 41 | Port Mirroring Examples – Ingress Monitoring                          |       |

| Figure 42 | Port Mirroring Examples – Egress Monitoring                           |       |

| Figure 43 | Typical Magic Packet Data Structure                                   |       |

| Figure 44 | Magic Packet Data Structure – Password Protection                     |       |

| Figure 45 | Time Stamp Event Location in the Frame                                |       |

| Figure 46 | Special Tag Location in the Frame                                     |       |

| Figure 47 | Timing Diagram for the GSW120 Reset Sequence                          |       |

| Figure 48 | Timing Diagram for the MDIO Interface                                 |       |

| Figure 49 | Timing Diagram for the SMDIO Interface                                | . 333 |

#### **List of Figures**

| Figure 50 | Transmit/Receive Timing Diagram of the RMII                            | 334 |

|-----------|------------------------------------------------------------------------|-----|

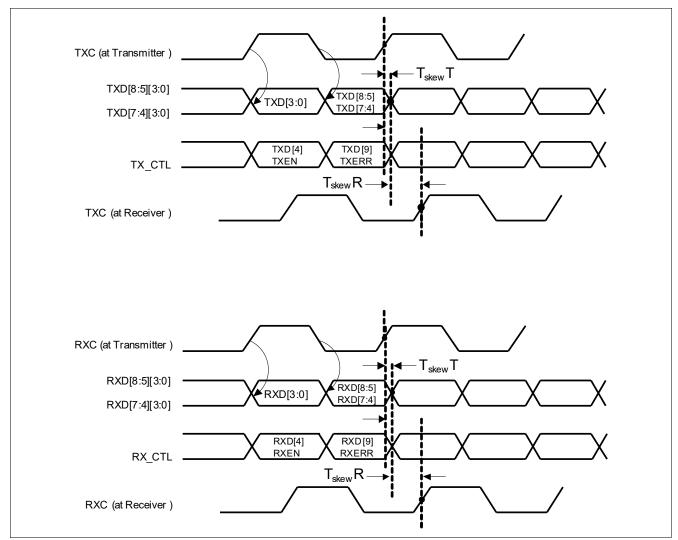

| Figure 51 | Timing Diagram of the RGMII                                            | 335 |

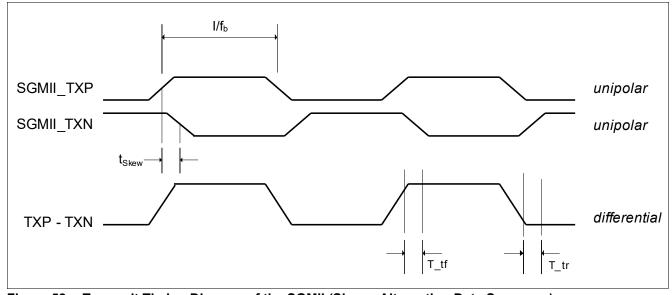

| Figure 52 | Transmit Timing Diagram of the SGMII (Shows Alternating Data Sequence) | 336 |

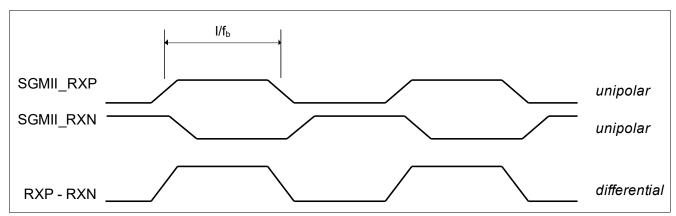

| Figure 53 | Receive Timing Diagram of the SGMII (Alternating Data Input Sequence)  | 337 |

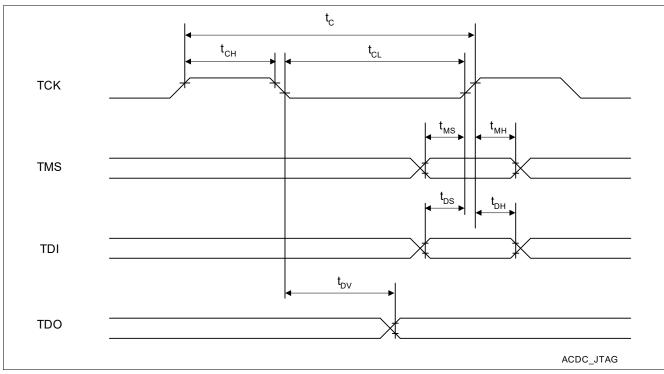

| Figure 54 | Test Interface Timing                                                  | 338 |

| Figure 55 | Schematic of a Transformer with CMC on Line                            | 339 |

| Figure 56 | Schematic of a Transformer with CMC on PHY Side                        | 340 |

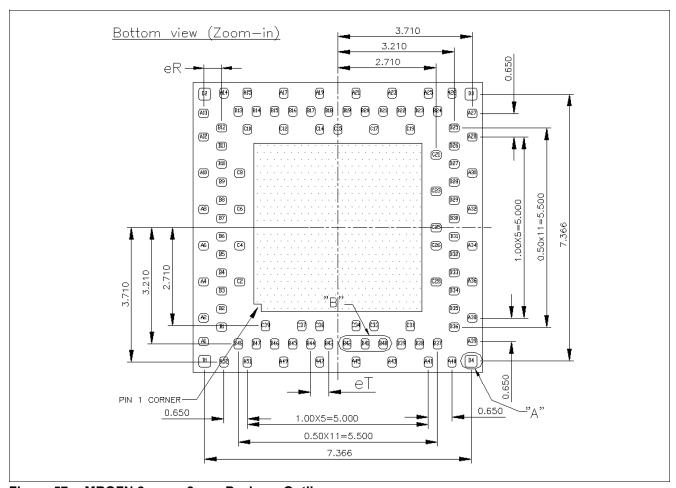

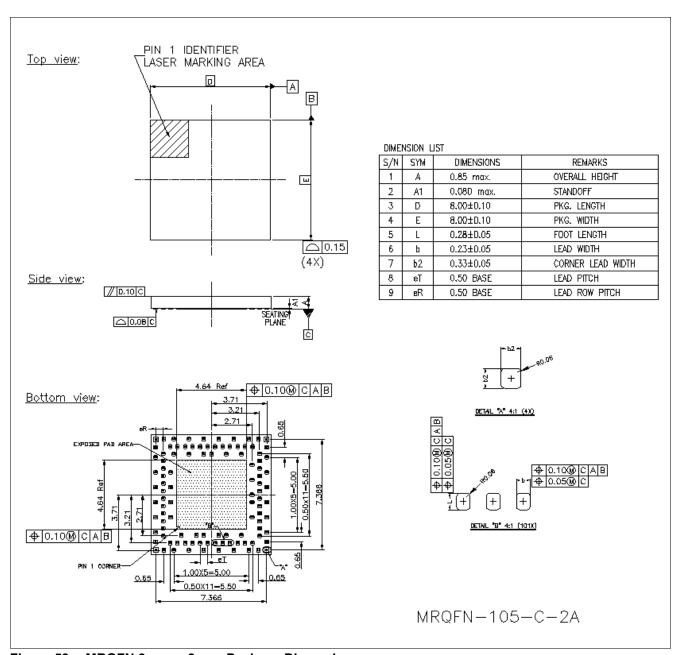

| Figure 57 | MRQFN 8 mm x 8 mm Package Outline                                      | 341 |

| Figure 58 | MRQFN 8 mm x 8 mm Package Dimensions                                   | 342 |

| Figure 59 | LGA 8 mm x 8 mm Package Outline                                        | 343 |

| Figure 60 | LGA 8 mm x 8 mm Package Dimensions                                     | 344 |

| Figure 61 | Example of Chip Marking                                                | 345 |

**List of Tables**

### **List of Tables**

| Table 1  | Abbreviations for Pin Type                                                        | 23  |

|----------|-----------------------------------------------------------------------------------|-----|

| Table 2  | Abbreviations for Buffer Type                                                     | 23  |

| Table 3  | Ethernet Media Interface Signals                                                  | 24  |

| Table 4  | SGMII Interface Signals                                                           | 25  |

| Table 5  | Ethernet Media Independent Interface Signals                                      | 25  |

| Table 6  | LED Interface Signals                                                             | 26  |

| Table 7  | Management Interface Signals                                                      | 29  |

| Table 8  | Miscellaneous Signals                                                             | 31  |

| Table 9  | Power Supply Pins                                                                 | 32  |

| Table 10 | Default Master MDIO Address Assignment                                            | 35  |

| Table 11 | Registers Configuration for Self-start Mode: Standalone Unmanaged Switch Sub-Mode | 44  |

| Table 12 | Registers Configuration for Self-start Mode: Managed Switch Sub-Mode              | 46  |

| Table 13 | LED Status VS LED Mode                                                            | 48  |

| Table 14 | EEPROM Type Record                                                                | 49  |

| Table 15 | Configuration Content Record: Incremental Access Format                           | 50  |

| Table 16 | Configuration Content Record: Single Access without Write Enable Format           |     |

| Table 17 | Configuration Content Record: Single Write Access with Write Enable Format        | 51  |

| Table 18 | Configuration Content Record: Run Self-start Mode Configuration Format            | 52  |

| Table 19 | Configuration Content Record: Wait Until True Format                              |     |

| Table 20 | Configuration Content Record: Conditional Jump Access Format                      | 52  |

| Table 21 | EEPROM Content Format                                                             |     |

| Table 22 | Functional Mode Pin Strapping                                                     |     |

| Table 23 | Pin Strapping Description                                                         | 54  |

| Table 24 | SUBTYPE Mode Configuration                                                        | 54  |

| Table 25 | Bit Rates                                                                         |     |

| Table 26 | MAC Learning Disable and MAC Learning Limitation Description                      |     |

| Table 27 | Port Settings                                                                     |     |

| Table 28 | CTAG VLAN Membership Table                                                        |     |

| Table 29 | Traffic Flow Table                                                                |     |

| Table 30 | Multicast Forwarding Decision                                                     | 91  |

| Table 31 | Multicast Host Messages                                                           |     |

| Table 32 | Multicast Router Messages                                                         |     |

| Table 33 | Typical IGMP/MLD Control Packets Forwarding Destination                           |     |

| Table 34 | IGMP/MLD Messages                                                                 |     |

| Table 35 | Typical IGMP/MLD Messages Forwarding Destination                                  |     |

| Table 36 | Resource Protection Options                                                       |     |

| Table 37 | Standard RMON Counters                                                            |     |

| Table 38 | Special Tag Ingress Format                                                        |     |

| Table 39 | Port Map Coding                                                                   |     |

| Table 40 | Traffic Class Map Coding                                                          |     |

| Table 41 | Special Tag Egress External Format (with Ethertype)                               |     |

| Table 42 | Special Tag Egress Internal Format (without Ethertype)                            |     |

| Table 43 | Error Codes                                                                       |     |

| Table 44 | Registers Overview                                                                |     |

| Table 45 | Register Access Types                                                             |     |

| Table 46 | Similar Registers                                                                 |     |

| Table 47 | Similar Registers                                                                 |     |

| Table 48 | Similar Registers                                                                 |     |

| Table 49 | Similar Registers                                                                 | 134 |

#### **List of Tables**

| Table 50 | Similar Registers                                                 | . 135 |

|----------|-------------------------------------------------------------------|-------|

| Table 51 | Similar Registers                                                 | . 136 |

| Table 52 | Similar Registers                                                 | . 137 |

| Table 53 | Similar Registers                                                 | . 160 |

| Table 54 | Similar Registers                                                 | . 166 |

| Table 55 | Similar Registers                                                 | . 192 |

| Table 56 | Registers Address Space                                           | . 223 |

| Table 57 | Registers Overview                                                | . 223 |

| Table 58 | Register Access Types                                             | . 225 |

| Table 59 | Registers Address Space                                           | . 268 |

| Table 60 | Registers Overview                                                | . 268 |

| Table 61 | Register Access Types                                             | . 269 |

| Table 62 | Registers Address Space                                           | . 306 |

| Table 63 | Registers Overview                                                | . 306 |

| Table 64 | Register Access Types                                             | . 307 |

| Table 65 | Similar Registers                                                 | . 318 |

| Table 66 | Similar Registers                                                 | . 319 |

| Table 67 | Similar Registers                                                 | . 322 |

| Table 68 | Similar Registers                                                 | . 323 |

| Table 69 | Absolute Limit Ratings                                            | . 325 |

| Table 70 | Operating Range                                                   | . 326 |

| Table 71 | Power Consumption                                                 | . 327 |

| Table 72 | DC Characteristics of the GPIO Interfaces (VDDP=3.3V)             | . 328 |

| Table 73 | DC Characteristics of the Transmit RGMII Interface                | . 328 |

| Table 74 | DC Characteristics of the Receive RGMII Interface                 | . 329 |

| Table 75 | AC Characteristics of the HRSTN Pin                               | . 330 |

| Table 76 | AC Characteristics of the Power Supply                            | . 331 |

| Table 77 | AC Characteristics of Input Clock on XTAL1 pin                    | . 331 |

| Table 78 | AC Characteristics of Output Clock on GPC pin                     | . 331 |

| Table 79 | Timing Characteristics of the MDIO Interface                      | . 332 |

| Table 80 | Timing Characteristics of the SMDIO Interface                     | . 333 |

| Table 81 | Timing Characteristics of the RMII at 100 Mbit/s                  | . 334 |

| Table 82 | Timing Characteristics of the RGMII                               | . 336 |

| Table 83 | Transmit Timing Characteristics of the SGMII                      | . 337 |

| Table 84 | Receive Timing Characteristics of the SGMII                       | . 337 |

| Table 85 | Test Interface Clock                                              | . 338 |

| Table 86 | JTAG Timing                                                       | . 338 |

| Table 87 | Specification of the Crystal                                      | . 339 |

| Table 88 | Electrical Characteristics for Supported Transformers (Magnetics) | . 340 |

| Table 89 | JEDEC Thermal Resistance PG-MRQFN-105 Package Parameters          | . 341 |

| Table 90 | JEDEC Thermal Resistance LGA-105 Package Parameters               | . 343 |

| Table 91 | Chip Marking Pattern                                              | . 345 |

| Table 92 | Product Naming                                                    | 345   |

#### 1 Product Overview

MaxLinear's Ethernet Switch GSW120 is a highly integrated, low-power, non-blocking four-port Gigabit Ethernet Switch with two tri-speed Ethernet PHYs, one four-speed SGMII interface, and one tri-speed RGMII interface. Switch ports 2 and 3 are unused. GSW120 uses a very small package, 8 mm x 8 mm, to minimize PCB size. There are two package variants available. For package details, see **Package Outline**.

Each Gigabit Ethernet (GbE) PHY supports 10BASE-Te, 100BASE-TX, and 1000BASE-T standards and is characterized by low power consumption. Support of Energy-Efficient Ethernet allows for even further reduction in idle mode power consumption. Power saving at the system level is also possible with the Wake-on-LAN feature. A low-EMI line driver with integrated termination facilitates a simplified PCB design.

The 5th port of the GSW120 supports a four-speed (10/100/1000/2500 Mbps) SGMII interface to connect to an external PHY, SFP stick, or the MAC of an external chip.

The 6th port of the GSW120 supports a tri-speed (10/100/1000 Mbps) RGMII interface to connect to an external PHY or the MAC of an external chip.

The GSW120 is configurable via pin strapping, MDIO interface, UART interface, SPI interface, or optionally by connecting an external EEPROM.

In addition, the 7th 802.3 Gigabit Ethernet MAC is integrated for packet insertion and extraction. This allows an external controller to transmit and receive Ethernet packets via the management interface.

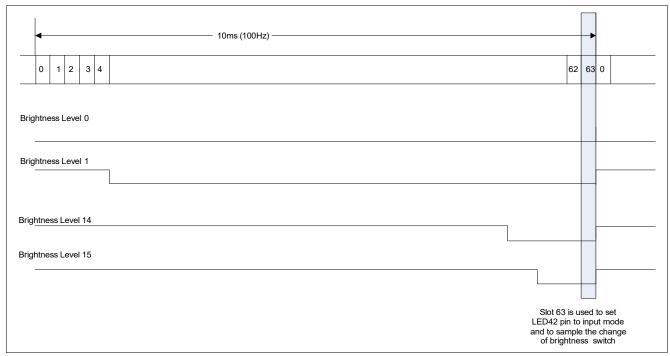

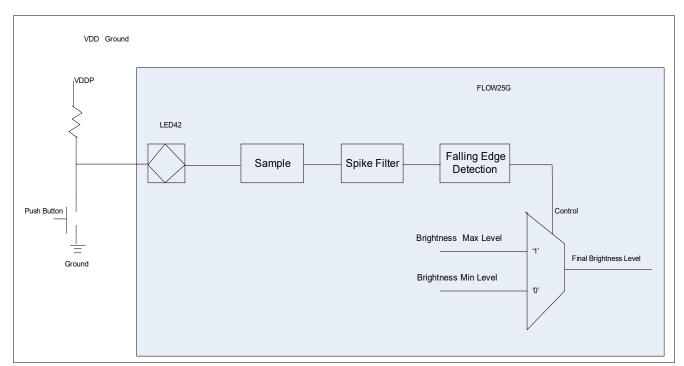

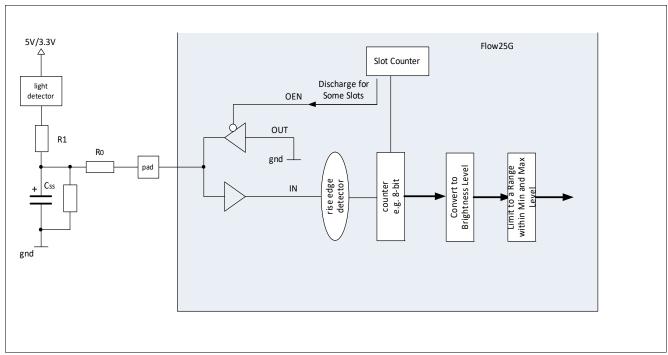

The GSW120 supports up to three LEDs per GbE PHY. Smart LED brightness control logic is integrated for power saving. LED brightness is either adjusted by a push button or varies dynamically depending on the intensity of the light measured by an external light sensor.

The 128 KB embedded packet storage SRAM is integrated and 9 KB jumbo frames are supported. The GSW120 integrates a 4K entry VLAN table for 802.1Q port-based, tag-based, and protocol based VLAN operation. It also supports double VLAN tagging, insertion, removal, and translation. The GSW120 features 2048 MAC addresses with 4-way hashing algorithm for address searching, auto-learning, and auto-aging.

Programmable parsing and a powerful classification engine allow future-proof designs that enable various data traffic types. The GSW120 supports IPv4 and IPv6 multicast forwarding, including IGMPv1/v2/v3 and MLD v1/v2 snooping.

The GSW120 features an advanced QoS architecture which prioritizes switch traffic for different classes of applications based on multiple fields of the packet. Multiple queues per port with strict or weighted round robin scheduling and rate shaping are supported. VLAN PCP and IP DSCP can be remarked. The GSW120 also supports Precise Time Stamping indication according to IEEE 1588v2 and IEEE 802.1AS.

Several degrees of application complexity are covered, from a basic stand-alone switch and set-top boxes to complex home gateways. The GSW120 is intended for Video/Audio applications in the Digital Home such as IP-TV, ADSL2+/VDSL2/PON IAD, Gateway, Wireless Router, Cable, Storage and HomePlug AV applications.

#### 1.1 Features

This section provides an overview of the basic Gigabit Ethernet Switch GSW120 functionality.

#### Interfaces

- Two multiple speed Ethernet PHY interfaces, compliant with:

- 10BASE-Te

- 100BASE-TX

- 1000BASE-T

- Auto-MDIX

- Auto-Downspeed

- Auto-Negotiation with Next Page Support

- Cable Diagnostics: Cable Open/Short Detection and Cable length estimation

- Test Loops and Analog Self Test

- Power Down Modes

- 802.3az Energy-Efficient Ethernet

- Support of Transformer-Less Ethernet for Backplane Applications

- · One set of RGMII interface:

- 10 Mbps, full and half duplex

- 100 Mbps, full and half duplex

- 1000 Mbps, full duplex

- · One set of RMII interface:

- RMII interface

- 100 Mbps, full and half duplex

- One set of SGMII Interface:

- Cisco\* Serial-GMII Specification Rev 1.8 standard compliant operation at 1.25 Gbaud/s; extensions to achieve 3.125 GBaud/s by overclocking

- 2.5 Gbps (one lane of XAUI conforming per 802.3, part 4, clause 47: 10 Gigabit Attachment Unit Interface (XAUI)) full duplex)

- SerDes interface includes Clock and Data Recovery (CDR)

- Multiple power-down modes

- Programmable TX attenuation and amplification

- Programmable flat-band RX equalization

- Auto-calibration of RX and TX impedances

- Test loop feature for debugging

- 10 Mbps, full and half duplex

- 100 Mbps, full and half duplex

- 1000 Mbps, full duplex

- 2500 Mbps, full duplex

- MDIO master interface to control external devices:

- Support auto polling of external PHY devices registers

- Support indirect access by command to external devices registers:

- Support programmable MDC clock up to 17 MHz

- SPI master interface connecting to a serial external E2PROM:

- Support programmable SPI clock up to 42 MHz

- Supports automatic switch configuration from an external E2PROM memory

- Support write access to E2PROM by an external controller

- Supports different E2PROM sizes from 1 kbits to 1024 kbits

- SPI Slave, MDIO slave or UART interface to allow control from an external microcontroller:

- Maximum MDIO interface clock: 25 MHz

- Maximum SPI interface clock: 12.5 MHz

- UART baud rate from 4800 to 921600

- JTAG boundary scan, test and debug interface

- Share pins with LED

- PHY status indicating LEDs:

- Directly attached

- Up to three LEDs per internal PHY port

- Configurable LED functions per LED (link/activity, duplex/collision, link speed etc)

- Steady/blinking indication

- LED brightness controlled by an external push button

- Up to 16 level LED brightness controlled by an external light sensor

- Twenty five general purpose IO: share pins with MDIO master interface, external interrupts, general purpose clock, SPI master interface, SPI slave interface, UART interface, MDIO slave, LED, JTAG functions.

#### Clocking

- Reference clock:

- 25 MHz or 40 MHz

- Crystal or direct input

- Two external clock outputs

#### **Ethernet MACs**

- Seven Ethernet MACs, complying with IEEE 802.3:

- Four rates, that is, 10 Mbps, 100 Mbps, 1000 Mbps and 2500 Mbps operation speed

- Half-duplex operation mode for 10 Mbps and 100 Mbps

- Full-duplex operation mode for all speed

- One dedicated Ethernet MAC is for packet insertion and extraction by an external controller via management interface

- Auto-negotiation for speed, duplex, flow control support, LPI support and link status

- Enhanced frame size support ("Jumbo frames", programmable limit up to 9 Kbyte)

- Flow control:

- Pause frame transmission/reception in full duplex mode

- Forced collisions in half-duplex mode

#### **Layer-2 Switching**

- · Store-and-forward architecture

- 1 Mbit on-chip segmented frame buffer

- 256 byte buffer seament size

- Up to 2048 MAC addresses:

- Multiple-bucket HASH algorithm storage

- Automatic learning and aging (1 s to 24 h)

- Manual learning (static entries)

- MAC learning limitation (configurable per port)

- MAC port locking and spoofing detection (configurable per port)

- MAC table freezing

- VLAN-unaware switching

- VLAN-aware switching:

- Shared VLAN learning

- Independent VLAN learning

- Up to 4096 VLAN IDs

- Port based VLAN

- MAC based VLAN with automatic learning

- Protocol-based VLAN based on flow classification result

- Double VLAN or VLAN QinQ, addition/removal/translation of Service Tag VLAN ID and Customer Tag VLAN

- Double VLAN or VLAN QinQ, port filtering based on both Service Tag VLAN ID and Customer Tag VLAN ID

- Multicast

- Up to 64 multicast groups

- Hardware IGMP mode: hardware based Join/Leave for IGMPv1/IGMPv2 mode, report suppression support

- Software IGMP mode: IGMPv1/v2/v3 and MLDv1/v2 Snooping

- Unknown IP multicast data stream forwarding or discard

- Any Source Multicast and Source Specific Multicast forwarding

#### Layer-2/3/4 Flow Classification

- Multi-field parsing and classification, for example based on:

- MAC source address

- MAC destination address

- Service Tag VLAN ID and Customer Tag VLAN ID

- Ethertype

- IPv4 header (DSCP, IP SA, IP DA)

- IPv6 header (DSCP, IP SA, IP DA)

- TCP source port/port range

- TCP destination port/port range

- UDP source port/port range

- UDP destination port/port range

- IGMP

- MLD

- ARP/RARP

- ICMP

- PPPoE, up to 16 session IDs

- 64 ACL rules

#### **Quality of Service**

- Up to 32 CoS (Class of Service) queues

- Configurable egress queue scheduling

- Strict priority

- Weighted fair queuing, with configurable weights

- Combination of strict priority and weighted fair queuing

- Flexible assignment of queues to egress ports

- Multiple queues can be assigned to a single port (as far as available from the global pool of queues)

- Maximum 16 queues per port

- Scalable egress rate shaping

- 32 rate shapers

- Up to 2 rate shapers can be assigned to a single queue (as far as available from global pool of rate shapers)

- Ingress traffic policing

- 16 traffic policers

- Standard single-rate Three Color Marker algorithm (srTCM)

- Color-aware/-unaware operation

- Policer can be assigned based on ingress port, egress port and flow classification result

- Remarking, Drop or Flow Control for non-conforming traffic

- Flexible QoS handling based on any flow classification result, for example (but not limited to)

- Service TAG VLAN PCP (Priority Code Point)

- Customer TAG VLAN PCP (Priority Code Point)

- IP DSCP

- Ingress port

- Source/destination IP address

- TCP/UDP port/port range

- Service Tag VLAN PCP and DEI remarking

- Customer Tag VLAN PCP remarking

- DSCP remarking

- Congestion management

- WRED algorithm (Weighted Random Early Discard)

- Buffer reservation

- Ingress port congestion based flow control

- Ingress port metering based flow control

- Three drop precedences

- Configurable thresholds

- AVB support

- Supports Precise Time Stamping indication according to IEEE P802.3bf for support of IEEE 1588v2, and IEEE 802.1AS

- Rate shaper can work either at Token Bucket Mode or Credit Based Mode

#### Security

- Access Control List (ACL)

- Use L2/L3/L4 flow classification results

- Blacklist

- Whitelist

- Access control actions

- Accept

- Discard

- Redirect

- Port Filtering

- Cross-state forwarding

- Cross-VLAN forwarding

- QoS classification

- VLAN Service Tag VLAN ID and Custom VLAN ID translation

- · Broadcast, unknown multicast and unknown unicast storm control

- Authentication support (IEEE 802.1X Port Authentication)

#### **Other Features**

- Spanning Tree/Rapid Spanning Tree and 16 STP instances per port

- Port trunking of any two ports

- Port mirroring

- 802.3az Energy-Efficient Ethernet

- Wake-on-LAN

- Detection of "magic packets"

- Check WoL password (optional)

- Wake-up interrupt to external device

- Special Tag

- Provides in-band packet control and status communication with an internal or external controller

- RMON counters

- Boundary Scan

#### **Power Supply**

- · Supply voltage domains

- 3.3 V for digital PAD except RGMII PAD

- 3.3 V for analog GPHY and SerDes

- 1.1 V for digital core

- 1.1 V for analog GPHY and SerDes

- 3.3 V or 2.5 V for digital RGMII PAD

#### 1.2 Applications

The following figures show application examples.

**Figure 1** and **Figure 2** show standalone switch applications with a SFP port. The main advantage for the SFP port is the flexibility for putting it in the network. SFP stands for "small form-factor pluggable" and is a hot-swappable input/output device that plugs into a Gigabit Ethernet port or slot, linking the port with the network. An optional external EEPROM is used for switch configuration. **Figure 1** shows an optional low cost brightness sensor integrated to allow the LED brightness to be controlled by the Gigabit Ethernet Switch to save the system power consumption. **Figure 2** shows an optional brightness on/off switch integrated to allow the LED brightness to be controlled by the switch button to save the system power consumption.

**Figure 3** shows an application of home gateway. An external SoC can manage the switch via management interface (eg. UART, SPI or MDIO interface). The 2.5 Gbps SGMII interface allows the high throughput rate between Ethernet LAN ports and SoC. In addition, another LAN/WAN type interface can be build (for example MoCA, Wi-Fi, Ethernet etc) and connected to the router/gateway SoC via a RGMII interface.

Figure 1 Standalone Desktop Switch with an Optional Brightness Sensor

Figure 2 Standalone Desktop Switch with an Optional Brightness Control Switch

Figure 3 Home Gateway

#### 1.3 Block Diagram

Figure 4 shows the block diagram.

Figure 4 Block Diagram

#### 2 External Signals

This chapter describes the signal mapping to the package.

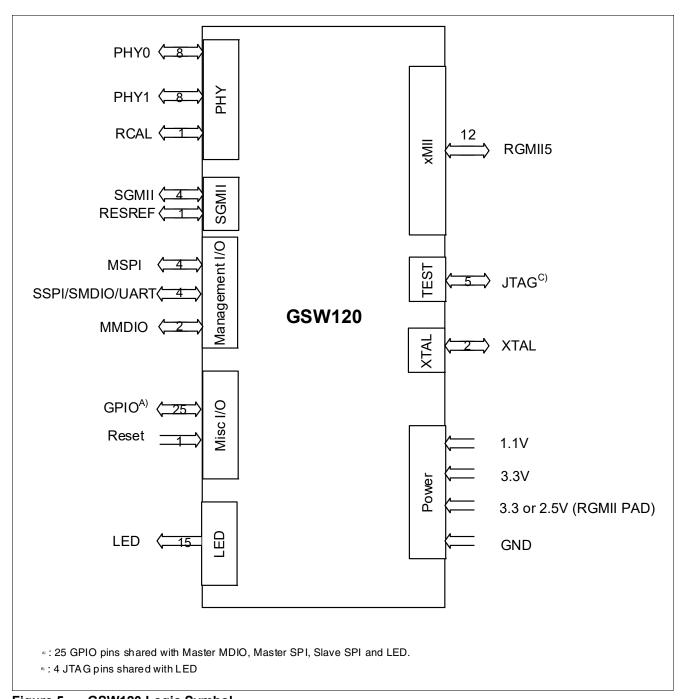

#### 2.1 Logic Symbol

Figure 5 gives a global overview of the device's external interfaces.

Figure 5 GSW120 Logic Symbol

#### 2.2 External Signal Description

This section provides in detail the pin diagrams, abbreviations for pin types and buffer types, as well as the table of input and output signals.

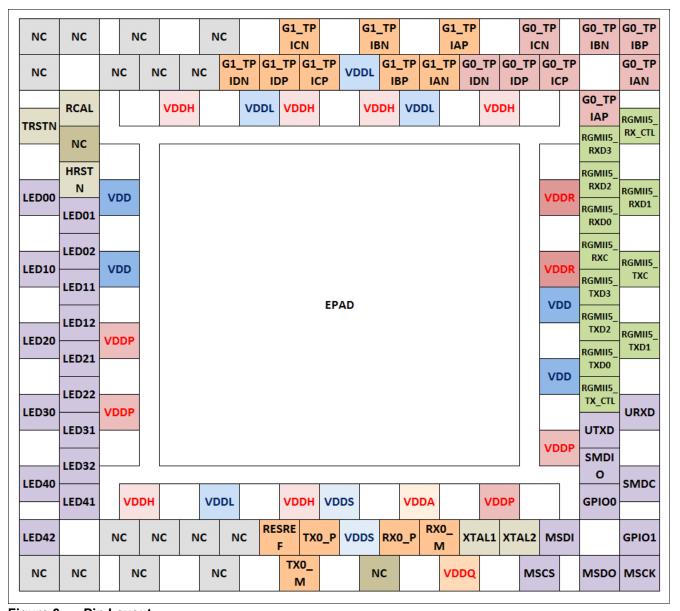

#### 2.2.1 Pin Diagram

Figure 6 shows the pin layout of the package.

Figure 6 Pin Layout

#### 2.2.2 Abbreviations

Table 1 and Table 2 summarize abbreviations used in the signal tables.

Table 1 Abbreviations for Pin Type

| Abbreviations | Description                                                                          |  |  |  |

|---------------|--------------------------------------------------------------------------------------|--|--|--|

| I             | Input-only, digital levels                                                           |  |  |  |

| 0             | Output-only, digital levels                                                          |  |  |  |

| I/O           | Bidirectional input/output signal, digital levels                                    |  |  |  |

| Prg           | Bidirectional pad, programmable to operate either as input or output, digital levels |  |  |  |

| Al            | Input-only, analog levels                                                            |  |  |  |

| AO            | Output-only, analog levels                                                           |  |  |  |

| AI/O          | Bidirectional, analog levels                                                         |  |  |  |

| PWR           | Power                                                                                |  |  |  |

| GND           | Ground                                                                               |  |  |  |

Table 2 Abbreviations for Buffer Type

| Abbreviations Description                                                                                                             |                                                                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LVTTL n                                                                                                                               | LVTTL characteristics, n = A, B, or C (driver strength)                                                                  |  |  |  |  |

| LVTTL n PU m                                                                                                                          | m LVTTL characteristics with weak pull-up device;<br>n = A, B, or C (driver strength); m = A, B, or C (pull-up strength) |  |  |  |  |

| LVTTL n PD m  LVTTL characteristics with weak pull-down device; n = A, B, or C (driver strength); m = A, B, or C (pull-down strength) |                                                                                                                          |  |  |  |  |

| LVTTL n OD LVTTL characteristics with open-drain characteristic, n = A, B, or C (driver street                                        |                                                                                                                          |  |  |  |  |

| LVTTL n PP LVTTL characteristics with push-pull characteristic, n = A, B, or C (driver streng                                         |                                                                                                                          |  |  |  |  |

| I <sup>2</sup> C bus characteristics, open drain, see the AC/DC specification for details.                                            |                                                                                                                          |  |  |  |  |

| A Analog characteristics, see the AC/DC specification for details.                                                                    |                                                                                                                          |  |  |  |  |

#### 2.2.3 Input/Output Signals

Table 3 to Table 8 show a detailed description of all pins.

#### 2.2.3.1 Ethernet Media Interface

Table 3 Ethernet Media Interface Signals

| Table 3 Ethernet Media Interrace Signals |                  |             |             |                                                        |

|------------------------------------------|------------------|-------------|-------------|--------------------------------------------------------|

| Pin No.                                  | Name             | Pin Type    | Buffer Type | Function                                               |

| Ethernet                                 | Port 0 Ethernet  | Media Inter | face        |                                                        |

| B36                                      | G0_TPIAP         | AI/AO       | Α           | Port 0 Transmit/Receive Positive/Negative              |

| A39                                      | G0_TPIAN         | AI/AO       | Α           | Connect directly to XFMR without any pull-down         |

| D4                                       | G0_TPIBP         | AI/AO       | Α           | terminators, such as resistors or capacitors, required |

| A40                                      | G0_TPIBN         | AI/AO       | Α           | - required                                             |

| B37                                      | G0_TPICP         | AI/AO       | Α           | _                                                      |

| A41                                      | G0_TPICN         | AI/AO       | Α           |                                                        |

| B38                                      | G0_TPIDP         | AI/AO       | Α           |                                                        |

| B39                                      | G0_TPIDN         | AI/AO       | Α           |                                                        |

| Ethernet                                 | Port 1 Ethernet  | Media Inter | face        |                                                        |

| A43                                      | G1_TPIAP         | AI/AO       | Α           | Port 1 Transmit/Receive Positive/Negative              |

| B40                                      | G1_TPIAN         | AI/AO       | Α           | Connect directly to XFMR without any pull-down         |

| B41                                      | G1_TPIBP         | AI/AO       | Α           | terminators, such as resistors or capacitors, required |

| A45                                      | G1_TPIBN         | AI/AO       | Α           |                                                        |

| B43                                      | G1_TPICP         | AI/AO       | Α           |                                                        |

| A47                                      | G1_TPICN         | AI/AO       | Α           |                                                        |

| B44                                      | G1_TPIDP         | AI/AO       | Α           |                                                        |

| B45                                      | G1_TPIDN         | AI/AO       | Α           |                                                        |

| Ethernet                                 | Port Calibration | 1           |             |                                                        |

| B1                                       | RCAL             | AI/AO       | Α           | Calibration for all GPHY Ethernet Ports                |

#### 2.2.3.2 SGMII Interface

Table 4 SGMII Interface Signals

| 1 4510 1 | 00     |             | oo olgila.     |                                                                                                                                                                                                                                                                                                                                                  |

|----------|--------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | Name   | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                         |

| B20      | RX0_P  | Al          | HD             | Differential SGMII Data Input Pair                                                                                                                                                                                                                                                                                                               |

| B21      | RX0_M  | Al          | HD             | These are the negative and positive signals respectively of the differential input pair of the SGMII SerDes interface. The pair samples a 1.25/3.125 GT/s differential data signal. These pins must be AC-coupled. Due to the integrated CDR, no external transmission peer source-synchronous clock is required. These pins must be AC-coupled. |

| B18      | TX0_P  | AO          | HD             | Differential SGMII Data Output Pair                                                                                                                                                                                                                                                                                                              |

| A19      | TX0_M  | AO          | HD             | These are the negative and positive signals respectively of the differential output pair of the SGMII SerDes interface. The pair samples a 1.25/3.125 GT/s differential data signal.                                                                                                                                                             |

| B17      | RESREF | AO          | А              | Pad to connect external tuning resistor                                                                                                                                                                                                                                                                                                          |

#### 2.2.3.3 Ethernet Media Independent Interface

Attention: The pin functionality in Table 5 highlighted in bold indicates the pin name.

Table 5

Ethernet Media Independent Interface Signals

| Pin No. | Name                                                    | Pin<br>Type | Buffer<br>Type                 | Function                                                                                                 |  |

|---------|---------------------------------------------------------|-------------|--------------------------------|----------------------------------------------------------------------------------------------------------|--|

| Etherne | t Port 5 Media Inde                                     | epende      | nt Inter                       | ace                                                                                                      |  |

| A34     | RGMII5_TXC<br>RMII5_REF_CLK                             | 0           | PD                             | RGMII: Transmit Clock for pins RGMII5_TX* RMII: REF_CLK (50 MHz. Programmable as either Output or Input) |  |

| B29     | RGMII5_TXD0<br>RMII5_TXD0                               | 0           |                                | RMII/RGMII Transmit Data Bit 0                                                                           |  |

| A32     | RGMII5_TXD1 O RMII/RGMII Transmit Data Bit 1 RMII5_TXD1 |             | RMII/RGMII Transmit Data Bit 1 |                                                                                                          |  |

| B30     | RGMII5_TXD2 O RGMII Transmit Data Bit 2                 |             | RGMII Transmit Data Bit 2      |                                                                                                          |  |

| B31     | RGMII5_TXD3                                             | 0           |                                | RGMII Transmit Data Bit 3                                                                                |  |

| B28     | RGMII5_TX_CTL<br>RMII5_TX_CTL                           | _           |                                | RMII/RGMII Transmit Control                                                                              |  |

| B32     | RGMII5_RXC                                              | I           | PD                             | RGMII Receive Clock for pins RGMII5_RX*                                                                  |  |

| B33     | RGMII5_RXD0<br>RMII5_RXD0                               | I           | PD                             | RMII/RGMII Receive Data Bit 0                                                                            |  |

| A36     | RGMII5_RXD1<br>RMII5_RXD1                               | I           | PD                             | RMII/RGMII Receive Data Bit 1                                                                            |  |

| B34     | RGMII5_RXD2                                             | I           | PD                             | RGMII Receive Data Bit 2                                                                                 |  |

Table 5 Ethernet Media Independent Interface Signals (cont'd)

| Pin No. | Name                          | Pin  | Buffer | Function                                                                                                                                                                                                                          |

|---------|-------------------------------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                               | Type | Type   |                                                                                                                                                                                                                                   |

| B35     | RGMII5_RXD3                   | 1    | PD     | RGMII Receive Data Bit 3                                                                                                                                                                                                          |

| A38     | RGMII5_RX_CTL<br>RMII5_CRS_DV | I    | PD     | RGMII: Receive Control RMII: Carrier Sense and Data Valid This is the carrier sense/data valid signal and encodes the RX_DV and CRS signals of the RMII, according to the RMII specification. The signal polarity is active high. |

#### 2.2.3.4 LED/UART/JTAG Interface

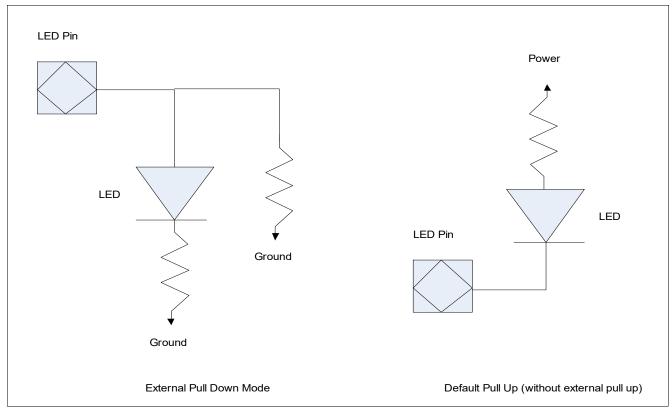

The LED interface is used to connect the external LEDs for Ethernet status indication of the Ethernet PHY interfaces. The single and dual color LEDs are supported. There are three LEDs per port. The JTAG interface shares the pins with the LED interface.

Attention: The pin functionality in Table 6 highlighted in bold indicates the pin name.

Table 6 LED Interface Signals

| Pin No. | Name   | Pin<br>Type | Buffer<br>Type                                                                                                                             | Function                                                                                                                                   |  |

|---------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| LED Sig | gnals  |             | -11                                                                                                                                        |                                                                                                                                            |  |

| ·       |        | Prg         | General Purpose IO 16 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull. |                                                                                                                                            |  |

|         | LED00  | 0           |                                                                                                                                            | LED0 for Port 0 LED control output, freely configurable, drives single-color or dual color LEDs.                                           |  |

| A6      | GPIO17 | Prg         | Prg                                                                                                                                        | General Purpose IO 17 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull. |  |

|         | LED10  | 0           |                                                                                                                                            | LED0 for Port 1 LED control output, freely configurable, drives single-color or dual color LEDs.                                           |  |

|         | TDO    | 0           |                                                                                                                                            | JTAG Serial Test Data Output JTAG test data output                                                                                         |  |

| A8      | GPIO18 | Prg         | Prg                                                                                                                                        | General Purpose IO 18 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull. |  |

|         | LED20  | 0           |                                                                                                                                            | Reserved                                                                                                                                   |  |

|         | TDI    | I           | PU                                                                                                                                         | JTAG Serial Test Data Input                                                                                                                |  |

| A10     | GPIO19 | Prg         | Prg                                                                                                                                        | General Purpose IO 19 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull. |  |

|         | LED30  | 0           |                                                                                                                                            | Reserved                                                                                                                                   |  |

|         | TMS    | I           | PU                                                                                                                                         | JTAG Test Mode Select                                                                                                                      |  |

Table 6 LED Interface Signals (cont'd)

| l able 6 | able 6 LED Interface Signals (confd) |             |                |                                                                                                                                                                                                                                                     |  |

|----------|--------------------------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.  | Name                                 | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                            |  |

| A12      | GPIO20                               | Prg         | Prg            | General Purpose IO 20 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

|          | TCK                                  | I           | PU             | JTAG Test Clock The signals TDI, TDO and TMS are synchronous subject to this JTAG test clock.  Note: When JTAG Controller is held in reset state, i.e. Gigabit Ethernet Switch operates in normal mode, this clock pin does not have to be clocked. |  |

| B4       | GPIO21                               | Prg         | Prg            | General Purpose IO 21 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

|          | LED01                                | 0           |                | LED1 for Port 0 LED control output, freely configurable, drives single-color or dual-color LEDs.                                                                                                                                                    |  |

| B6       | GPIO22                               | Prg         | Prg            | General Purpose IO 22 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

|          | LED11                                | 0           |                | LED1 for Port 1 LED control output, freely configurable, drives single-color or dual-color LEDs.                                                                                                                                                    |  |

| B8       | GPIO23                               | Prg         | Prg            | General Purpose IO 23 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

|          | LED21                                | 0           |                | Reserved                                                                                                                                                                                                                                            |  |

| B10      | GPIO24                               | Prg         | Prg            | General Purpose IO 24 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

|          | LED31                                | 0           |                | Reserved                                                                                                                                                                                                                                            |  |

| B12      | GPIO25                               | Prg         | Prg            | General Purpose IO 25 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.                                                                                                          |  |

| B5       | GPIO26                               | Prg         | Prg            | General Purpose IO 26 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.  Note: This pin reads in pin-strapping information during reset.                                         |  |

|          | LED02                                | 0           |                | LED2 for Port 0 LED control output, freely configurable, drives dual-color or single color LED.                                                                                                                                                     |  |

|          | LIGHT                                | I/O         |                | Light Sensor Input Light Sensor Input                                                                                                                                                                                                               |  |

Table 6 LED Interface Signals (cont'd)

| Pin No. | Name           | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                    |  |

|---------|----------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B7      | GPIO27 Prg Prg |             | Prg            | General Purpose IO 27 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.  Note: This pin reads in pin-strapping information during reset. |  |

|         | LED12          | 0           |                | LED2 for Port 1 LED control output, freely configurable, drives dual-color or single color LED.                                                                                                             |  |

| B9      | GPIO28         | Prg         | Prg            | General Purpose IO 28 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.  Note: This pin reads in pin-strapping information during reset. |  |

|         | LED22          | 0           |                | Reserved                                                                                                                                                                                                    |  |

| B11     | GPIO29         | Prg         | Prg            | General Purpose IO 29 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.  Note: This pin reads in pin-strapping information during reset. |  |

|         | LED32          | 0           |                | Reserved                                                                                                                                                                                                    |  |

| A13     | GPIO30         | Prg         | Prg            | General Purpose IO 30 It can be selected as input or output mode. The output characteristic can be selected to be open drain or push-pull.  Note: This pin reads in pin-strapping information during reset. |  |

|         | LED42          | I/O         |                | Brightness Control This pin is used for the brightness control switch input.                                                                                                                                |  |