# This document has been made public and no NDA is needed.

The "Confidential" statement in the attached material is no longer valid and may be disregarded.

This document falls into one of these categories:

# 1. Document has MaxLinear branding

The "MaxLinear Confidential" statement will be removed from the document upon its next revision

# 2. Document has non-MaxLinear branding

In 2020, MaxLinear acquired the Connected Home Division business of Intel Corporation, including the former Intel<sup>®</sup> product/s referenced in the title of the attached material. The MaxLinear logo will be added to the attached material upon its next revision. MaxLinear is now the manufacturer of this product.

Direct any questions and product support requests to your MaxLinear sales contact, MaxLinear Sales Representative or Distributor, or login to your myMxL account and create a new support ticket.

Corporate Headquarters: 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, and any MaxLinear trademarks, MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, AnyWAN and the MaxLinear logo are all on the products sold, are all trademarks of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

# **Ethernet Network Connection**

# Single Port 2.5G Ethernet PHY

Ethernet Network Connection GPY211 (GPY211B1VC, GPY211C0VC)

# Data Sheet

MaxLinear Confidential

Revision 1.4, 2021-04-27 Reference ID 617810

# Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

MaxLinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

\*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2021 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008 Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

### **Revision History**

| Current:<br>Previous: | Revision 1.4, 2021-04-27<br>Revision 1.3, 2020-12-22                                                                                        |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Page                  | Major changes since previous revision                                                                                                       |  |  |  |  |  |

| All                   | This document covers GPY211C0VC and GPY211B1VC. GPY211C0VC is an enhanced performance version of GPY211B1VC with reduced power consumption. |  |  |  |  |  |

| 1                     | Added GPY211C0VC on Front Page.                                                                                                             |  |  |  |  |  |

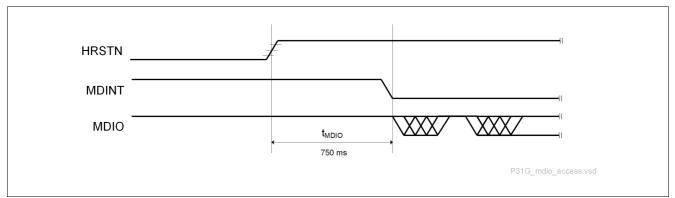

| 26                    | Figure 4, MDIO Access Timing: Added MDIO access timing.                                                                                     |  |  |  |  |  |

| 37                    | Section 3.4.7.1 Enabling SGMII Auto-negotiation Mode: Corrected SGMII auto-negotiation default setting.                                     |  |  |  |  |  |

| 40                    | Section 3.5.3 LED Brightness Control: Updated LED Brightness Control section.                                                               |  |  |  |  |  |

| 80                    | Removed TPG Control register.                                                                                                               |  |  |  |  |  |

| 122                   | Table 23, Registers Overview: Updated ANEG_MGBT_AN_CTRL Reset value.                                                                        |  |  |  |  |  |

| 135                   | ANEG_MGBT_AN_CTRL, MULTI GBT AN Control Register (Register 7.32): Updated Reset value.                                                      |  |  |  |  |  |

| 142                   | VSPEC1_LED0, PULSE: Updated Pulsing Configuration.                                                                                          |  |  |  |  |  |

| 143                   | VSPEC1_LED1, PULSE: Updated Pulsing Configuration.                                                                                          |  |  |  |  |  |

| 144                   | VSPEC1_LED2, PULSE: Updated Pulsing Configuration.                                                                                          |  |  |  |  |  |

| 146                   | VSPEC1_LED3, PULSE: Updated Pulsing Configuration.                                                                                          |  |  |  |  |  |

| 152                   | Updated conversion formula in temperature code.                                                                                             |  |  |  |  |  |

| 163                   | Table 28, Typical Power Consumption (GPY211C0VC): Added typical power consumption for GPY211C0VC.                                           |  |  |  |  |  |

| 164                   | Table 30, Maximum Power Consumption (GPY211C0VC): Added maximum power consumption for GPY211C0VC.                                           |  |  |  |  |  |

| 185                   | Figure 31, Example of Chip Marking: Updated Chip Marking pattern.                                                                           |  |  |  |  |  |

| 185                   | Table 53, Chip Marking Pattern: Updated Chip Marking Pattern information.                                                                   |  |  |  |  |  |

| 185                   | Table 54, Product Naming (GPY211C0VC): Added Product Naming for GPY211C0VC, including engineering sample information.                       |  |  |  |  |  |

# Ethernet Network Connection GPY211 (GPY211B1VC, GPY211C0VC)

### **Table of Contents**

# **Table of Contents**

|            | Table of Contents                                    | . 4 |

|------------|------------------------------------------------------|-----|

|            | List of Figures                                      | . 7 |

|            | List of Tables                                       | . 8 |

| 1          | Product Overview                                     | 10  |

| 1.1        | Features                                             |     |

| 1.2        | Block Diagram                                        | 13  |

| 2          | External Signals                                     | 14  |

| 2.1        | Overview                                             |     |

| 2.2        | External Signal Description                          | 15  |

| 2.2.1      | Pin Diagram                                          | 15  |

| 2.2.2      | Abbreviations                                        | 16  |

| 2.2.3      | Input/Output Signals                                 |     |

| 2.2.3.1    | Ethernet Media Interface                             |     |

| 2.2.3.2    | SGMII Interface                                      |     |

| 2.2.3.3    | LED/JTAG/GPIO Interface                              |     |

| 2.2.3.4    | Management Interfaces                                |     |

| 2.2.3.5    | Miscellaneous Signals                                |     |

| 2.2.3.6    | Power Supply                                         |     |

| 3          | Functional Description                               |     |

| 3.1        | Power Supply, Clock and Reset                        |     |

| 3.1.1      | Power Supply                                         |     |

| 3.1.2      | Clock Generation                                     |     |

| 3.1.3      | Reset Generation                                     |     |

| 3.1.4      | Power-On Sequence                                    |     |

| 3.1.5      | Configuration by Pin Strapping                       |     |

| 3.2<br>3.3 | Configuration via MDIO Management Interface          |     |

| 3.3.1      | Twisted Pair Interface                               |     |

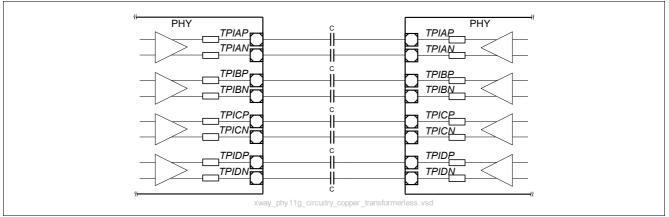

| 3.3.2      | Transformerless Ethernet (TLE)                       |     |

| 3.3.3      | Auto-negotiation (ANEG)                              |     |

| 3.3.4      | Auto-downspeed                                       |     |

| 3.3.5      | Polarity Reversal Correction                         |     |

| 3.3.6      | Auto-Crossover Correction                            |     |

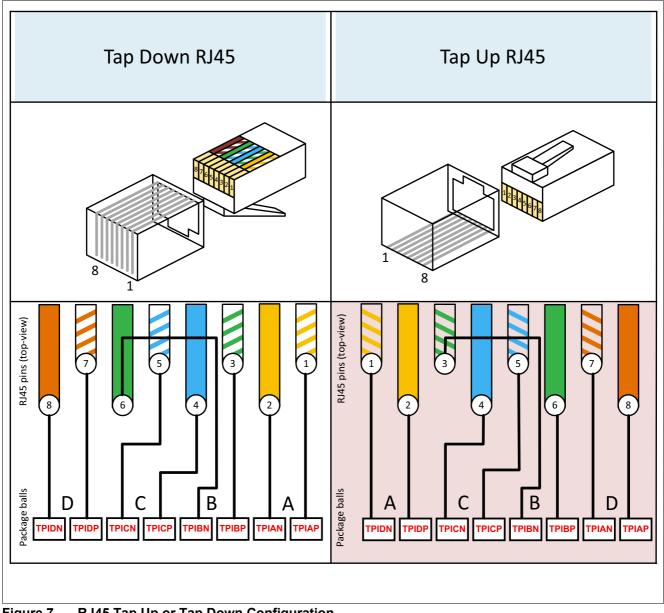

| 3.3.7      | RJ45 Tap Up or Tap Down Configuration                |     |

| 3.3.8      | Wake-on-LAN (WoL)                                    |     |

| 3.4        | SGMII Interface                                      |     |

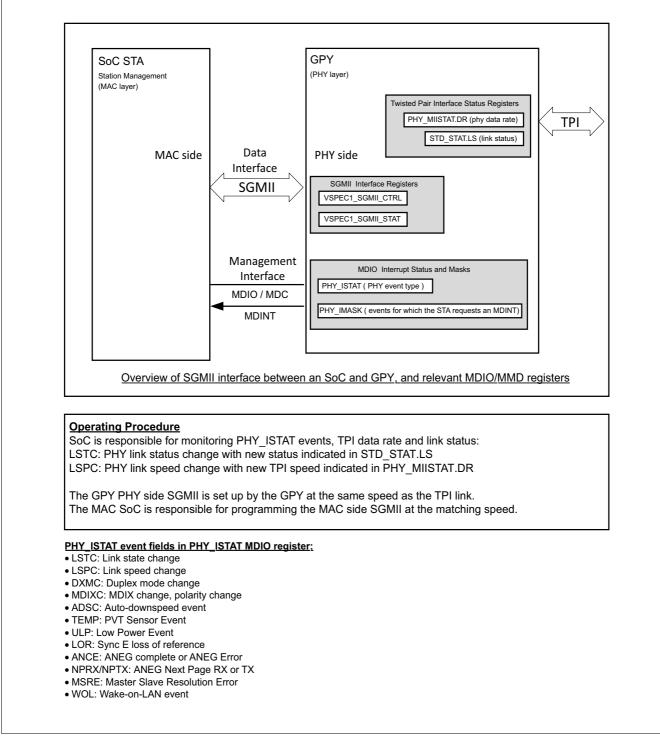

| 3.4.1      | SGMII Control and Status Registers                   | 32  |

| 3.4.2      | SGMII Configuration at Power Up                      | 34  |

| 3.4.3      | SGMII PHY Side Setup According to TPI Setup          | 34  |

| 3.4.4      | SGMII PHY Side Setup Fixed irrespective to TPI Setup | 34  |

| 3.4.5      | SGMII MAC Side Setup by MAC SoC                      | 34  |

| 3.4.6      | SGMII Link Monitoring by MAC SoC                     | 35  |

| 3.4.6.1    | Actions on TPI Link Down / Link Up Status Change     |     |

| 3.4.6.2    | New TPI Link Up at Same Speed                        |     |

| 3.4.6.3    | Change of Speed After a New Link Up on TPI           |     |

| 3.4.7      | Auto-negotiation Modes Supported by SGMII            |     |

| 3.4.7.1    | Enabling SGMII Auto-negotiation Mode                 | 37  |

# Ethernet Network Connection GPY211 (GPY211B1VC, GPY211C0VC)

### **Table of Contents**

| 3.5<br>3.5.1 | LED Interface                                    |     |

|--------------|--------------------------------------------------|-----|

| 3.5.2        |                                                  |     |

| 3.5.3        |                                                  |     |

| 3.6          | Precision Time Protocol (PTP) Feature            |     |

| 3.6.1        | PTP Feature Purpose                              |     |

| 3.6.2        | PTP Feature Configuration                        |     |

| 3.7          | Pulse Per Second (PPS) Feature                   |     |

| 3.7.1        | PPS Feature Purpose                              |     |

| 3.7.2        | PPS Feature Configuration                        |     |

| 3.8          | Smart-AZ Feature                                 |     |

| 3.9          | Power Management                                 |     |

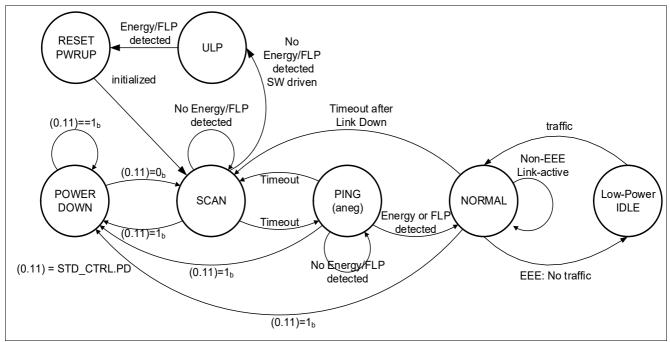

| 3.9.1        | Power States                                     |     |

| 3.9.2        | RESET Power Up                                   |     |

| 3.9.3        | SLEEP State                                      |     |

| 3.9.4        | SCAN State                                       |     |

| 3.9.5        | PING State                                       | 44  |

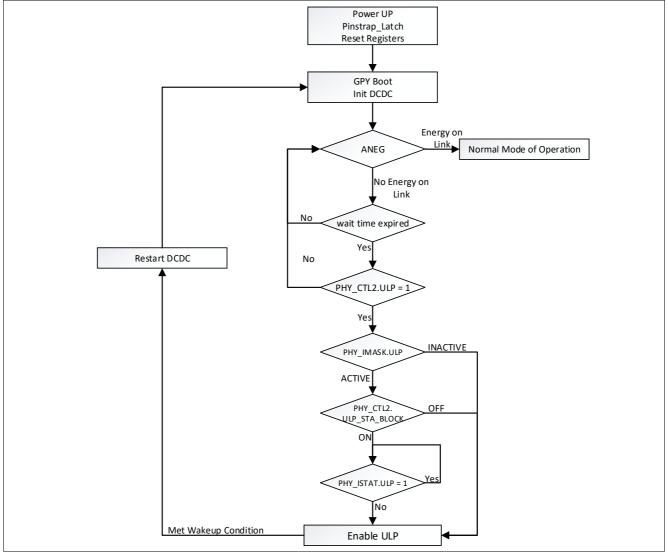

| 3.9.6        | ULP State                                        | 44  |

| 3.9.7        | NORMAL State                                     | 47  |

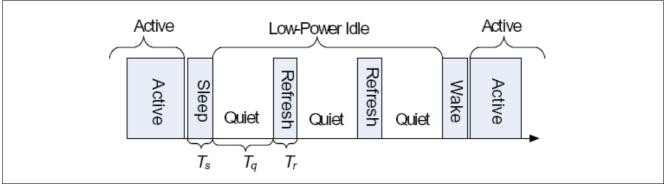

| 3.9.8        | Low-Power IDLE State: Energy-Efficient Ethernet  | 47  |

| 3.10         | Field Firmware Upgrade (FFU)                     | 47  |

| 4            | MDIO and MMD Register Interface Description      | 49  |

| 4.1          | Definitions                                      |     |

| 4.2          | Register Naming and Numbering                    |     |

| 4.2.1        | Register Numbering                               |     |

| 4.2.2        | Register Naming                                  |     |

| 4.2.3        | Examples                                         |     |

| 4.3          | MMD Devices Present in GPY211                    |     |

| 4.4          | Responsibilities of the STA                      |     |

| 4.5          | MDIO Access Protocols to Read / Write Registers  |     |

|              | -                                                |     |

| 5            | MDIO Registers Detailed Description              |     |

| 5.1          | Standard Management Registers                    |     |

| 5.1.1        | Standard Management Registers                    |     |

| 5.2          | GPY-specific Management Registers                |     |

| 5.2.1        | GPY-specific Management Registers                | 70  |

| 6            | MMD Registers Detailed Description               | 84  |

| 6.1          | Standard PMAPMD Registers for MMD=0x01           |     |

| 6.1.1        | Standard PMAPMD Registers for MMD=0x01           |     |

| 6.2          | Standard PCS Registers for MMD=0x03              |     |

| 6.2.1        | Standard PCS Registers for MMD=0x03              |     |

| 6.3          | Standard Auto-Negotiation Registers for MMD=0x07 |     |

| 6.3.1        | Standard Auto-Negotiation Registers for MMD=0x07 |     |

| 6.4          | Vendor Specific 1 Device for MMD=0x1E            |     |

| 6.4.1        | Vendor Specific 1 Device for MMD=0x1E            |     |

| 6.5          | Vendor Specific 2 Device for MMD=0x1F            |     |

| 6.5.1        | Vendor Specific 2 Device for MMD=0x1F            |     |

|              |                                                  |     |

| 7            | Electrical Characteristics                       |     |

| 7.1          | Absolute Maximum Ratings                         |     |

| 7.2          | Operating Range                                  |     |

| 7.3          | Chip Power Consumption                           | 163 |

### **Table of Contents**

| 7.4     | DC Characteristics                                                               | 165 |

|---------|----------------------------------------------------------------------------------|-----|

| 7.4.1   | Digital Interfaces                                                               | 165 |

| 7.4.2   | Twisted Pair Interface                                                           | 165 |

| 7.4.3   | Built-in Temperature Sensor                                                      | 166 |

| 7.5     | AC Characteristics                                                               | 167 |

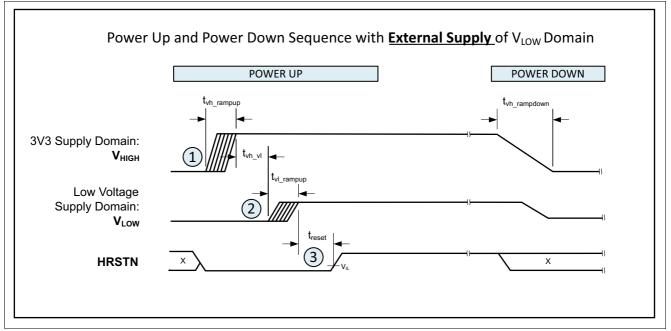

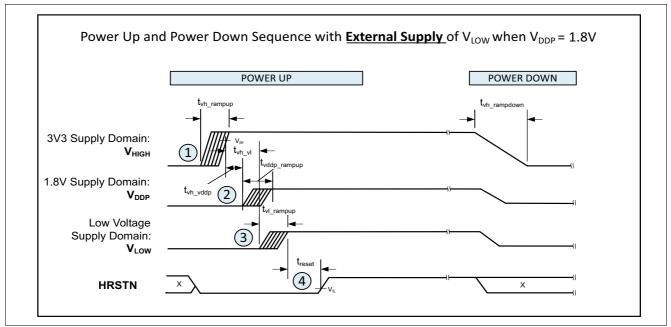

| 7.5.1   | Power Up and Power Down Sequence with External Supply of V <sub>LOW</sub> Domain | 167 |

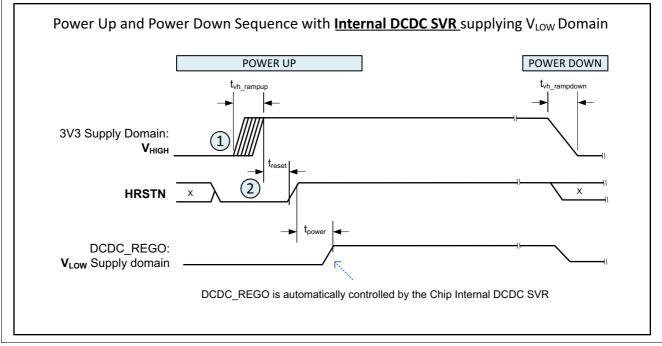

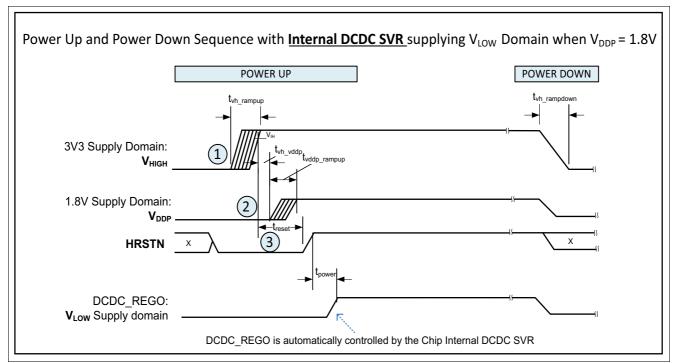

| 7.5.2   | Power Up and Power Down Sequence in Internal DCDC SVR Configuration              | 169 |

| 7.5.3   | Power Supply Rail Requirements                                                   | 171 |

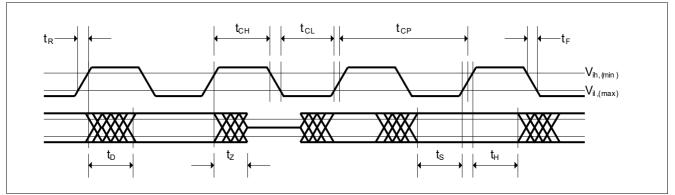

| 7.5.4   | MDIO Interface                                                                   | 172 |

| 7.5.5   | SGMII Interface                                                                  | 173 |

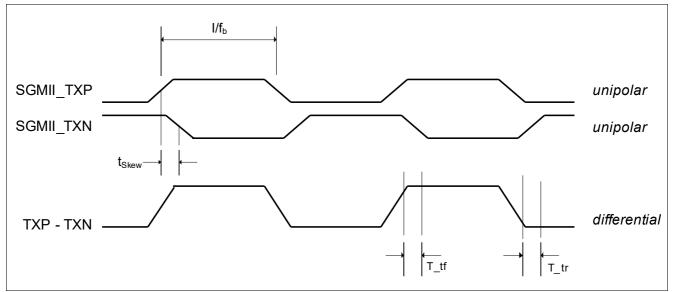

| 7.5.5.1 | Transmit Timing Characteristics                                                  | 173 |

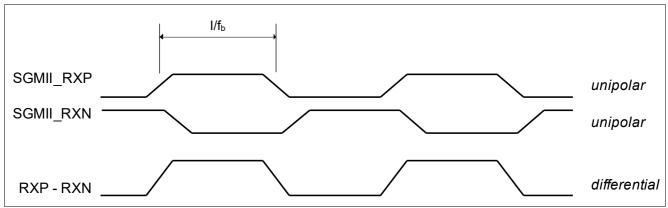

| 7.5.5.2 | Receive Timing Characteristics                                                   | 174 |

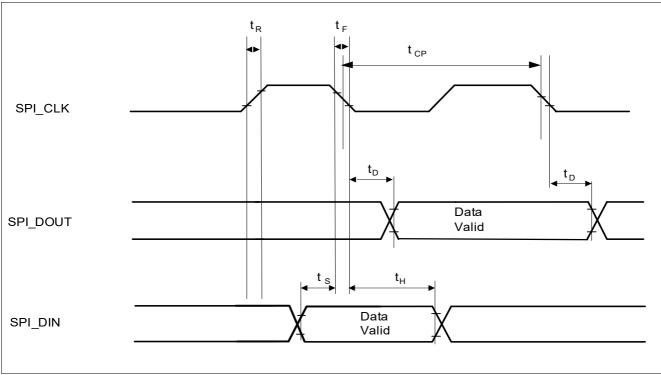

| 7.5.6   | Serial Peripheral Interface (SPI)                                                | 175 |

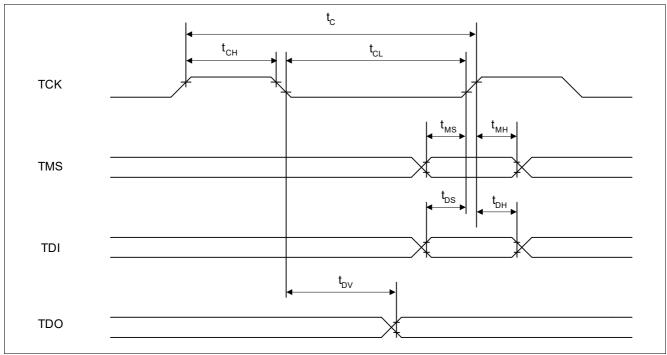

| 7.5.7   | JTAG Interface                                                                   | 176 |

| 7.5.8   | Crystal Specification                                                            | 177 |

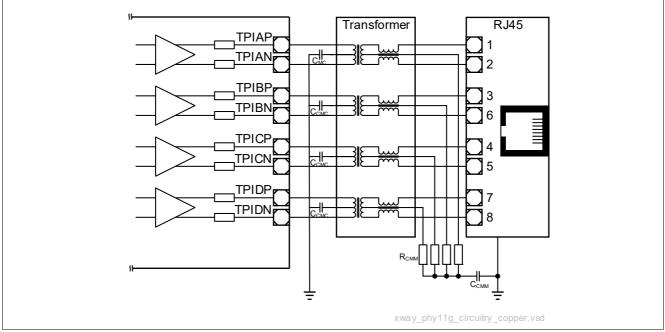

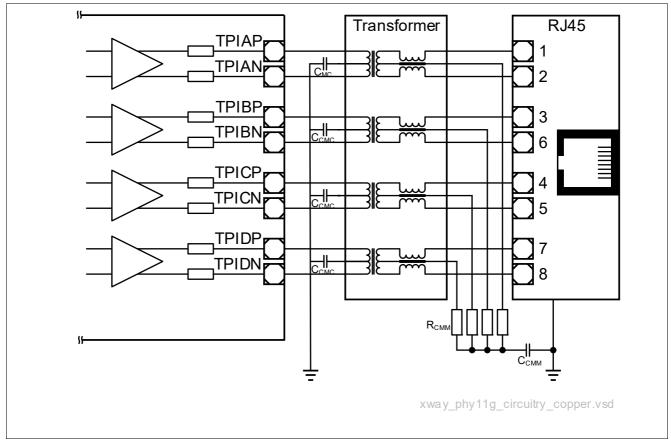

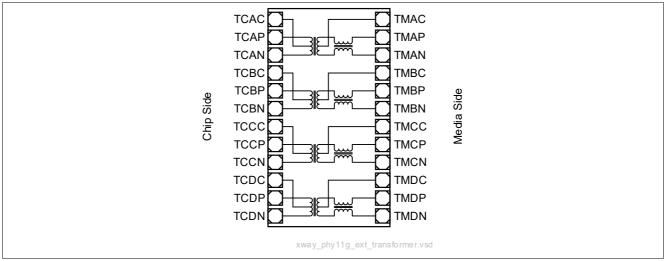

| 7.6     | External Circuitry                                                               | 178 |

| 7.6.1   | Twisted-Pair Common-Mode Rejection and Termination Circuitry                     | 178 |

| 7.6.2   | Transformer (Magnetics)                                                          | 179 |

| 7.6.3   | RJ45 Plug                                                                        | 180 |

| 7.6.4   | Calibration Resistors                                                            | 180 |

| 7.7     | Power Supply                                                                     | 180 |

| 7.7.1   | Power Supply Using Integrated DC/DC SVR Converter                                | 180 |

| 7.7.2   | Power Supply without using Integrated DC/DC Converter                            | 182 |

| 8       | Package Outline                                                                  | 183 |

| 8.1     | Chip Identification and Ordering Information                                     |     |

|         | Terminology                                                                      | 186 |

|         | References                                                                       | 189 |

**List of Figures**

# List of Figures

| Figure 1  | Ethernet Network Connection GPY211 Block Diagram                                                                  | 13 |

|-----------|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | Ethernet Network Connection GPY211 External Signals Overview                                                      | 14 |

| Figure 3  | Pin Diagram for PG-VQFN-56 (Top View)                                                                             | 15 |

| Figure 4  | MDIO Access Timing                                                                                                | 26 |

| Figure 5  | Twisted-Pair Interface of GPY211 Including Transformer and RJ45 Plug                                              | 27 |

| Figure 6  | External Circuitry for the Transformerless Ethernet Application                                                   | 27 |

| Figure 7  | RJ45 Tap Up or Tap Down Configuration.                                                                            | 30 |

| Figure 8  | Block Diagram of WoL Application                                                                                  | 31 |

| Figure 9  | GPY211 SGMII Configuration and Status Registers                                                                   | 33 |

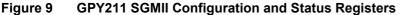

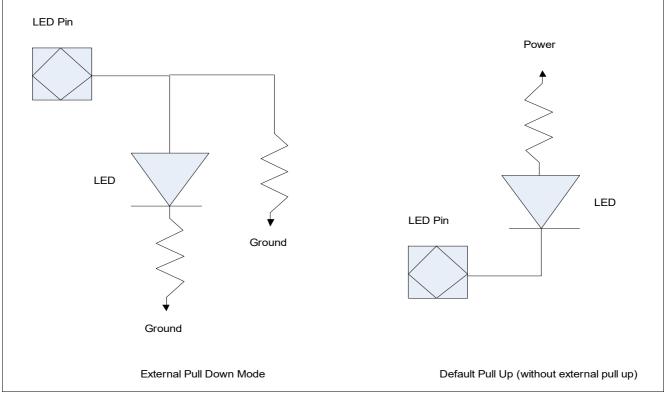

| Figure 10 | LED Connection Options to Ground or Power Supply                                                                  |    |

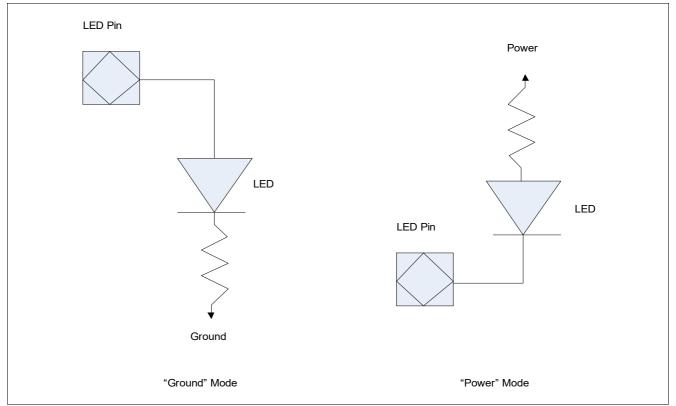

| Figure 11 | Connection of a Dual Color LED and Configuring Pin Strap Value                                                    | 39 |

| Figure 12 | Connection of a Single Color LED and Configuring Pin Strap Value                                                  |    |

| Figure 13 | LED Brightness Control By Controlling LED Output Enable/Disable                                                   | 40 |

| Figure 14 | State Diagram for Power Down State Management.                                                                    | 43 |

| Figure 15 | ULP Sequence                                                                                                      | 45 |

| Figure 16 | EEE Low-Power Idle Sequence                                                                                       | 47 |

| Figure 17 | Timing Diagram for the Reset Sequence (External supply of V <sub>LOW</sub> domain) 1                              | 67 |

| Figure 18 | Timing Diagram for the Reset Sequence (External supply of V <sub>LOW</sub> domain) when V <sub>DDP</sub> =1.8 V 1 | 68 |

| Figure 19 | Timing Diagram for the Reset Sequence (Internal DCDC SVR Configuration) 1                                         | 69 |

| Figure 20 | Timing Diagram for the Reset Sequence (Internal DCDC SVR Configuration) when V <sub>DDP</sub> =1.8 V 1            | 70 |

| Figure 21 | Timing Diagram for the MDIO Interface 1                                                                           | 72 |

| Figure 22 | Transmit Timing Diagram of the SGMII (shows alternating data sequence) 1                                          | 73 |

| Figure 23 | Receive Timing Diagram of the SGMII (alternating data input sequence)                                             | 74 |

| Figure 24 | SPI Master Interface Timing 1                                                                                     | 75 |

| Figure 25 | JTAG Interface Timing 1                                                                                           | 76 |

| Figure 26 | Twisted Pair Common-Mode Rejection and Termination Circuitry                                                      | 78 |

| Figure 27 | Schematic of an Ethernet Transformer Device 1                                                                     | 79 |

| Figure 28 | External Circuitry Using the Integrated DC/DC Converter                                                           | 81 |

| Figure 29 | External Circuitry without using the Integrated DC/DC Converter                                                   | 82 |

| Figure 30 | PG-VQFN-56 7 mm x 7 mm Package Outline 1                                                                          |    |

| Figure 31 | Example of Chip Marking 1                                                                                         | 85 |

## Ethernet Network Connection GPY211 (GPY211B1VC, GPY211C0VC)

### List of Tables

# **List of Tables**

| Table 1  | Abbreviations for Pin Type                                                     | . 16 |

|----------|--------------------------------------------------------------------------------|------|

| Table 2  | Abbreviations for Buffer Type                                                  | . 16 |

| Table 3  | Ethernet Media Interface Signals                                               | . 17 |

| Table 4  | SGMII Interface Signals                                                        | . 17 |

| Table 5  | LED Interface Signals                                                          | . 18 |

| Table 6  | Management Interface Signals                                                   | . 19 |

| Table 7  | Miscellaneous Signals                                                          | . 20 |

| Table 8  | Power Supply Pins                                                              | . 21 |

| Table 9  | Device Ground                                                                  | . 23 |

| Table 10 | Pin Names used for Pin Strapping                                               | . 25 |

| Table 11 | Pin Strapping Configuration Description                                        | . 25 |

| Table 12 | Supported Twisted Pair Mappings on a CAT5 or Better Cable                      | . 29 |

| Table 13 | Programming Sequence for the Wake-on-LAN Functionality                         | . 31 |

| Table 14 | ULP State Entry and Exit Sequence                                              | . 45 |

| Table 15 | ULP Persistent Registers                                                       |      |

| Table 16 | MDIO / MMD Devices Present in GPY211                                           | . 51 |

| Table 17 | Register Access Type                                                           | . 52 |

| Table 18 | Registers Overview                                                             | . 53 |

| Table 19 | Registers Overview                                                             | . 70 |

| Table 20 | Register Access Type                                                           | . 84 |

| Table 21 | Registers Overview                                                             | . 85 |

| Table 22 | Registers Overview                                                             | 109  |

| Table 23 | Registers Overview                                                             | 122  |

| Table 24 | Registers Overview                                                             | 141  |

| Table 25 | Registers Overview                                                             | 156  |

| Table 26 | Absolute Maximum Ratings                                                       | 160  |

| Table 27 | Operating Range                                                                |      |

| Table 28 | Typical Power Consumption (GPY211C0VC)                                         |      |

| Table 29 | Typical Power Consumption (GPY211B1VC).                                        |      |

| Table 30 | Maximum Power Consumption (GPY211C0VC)                                         |      |

| Table 31 | Maximum Power Consumption (GPY211B1VC)                                         |      |

| Table 32 | DC Characteristics of the GPIO Interfaces (VDDP = 3.3 V)                       |      |

| Table 33 | DC Characteristics of the GPIO Interfaces (VDDP = 1.8 V)                       |      |

| Table 34 | Temperature Sensor Characteristics                                             |      |

| Table 35 | Power Supply Timings (External supply of V <sub>LOW</sub> domain)              |      |

| Table 36 | Power Supply Timings (Internal DCDC SVR Configuration)                         |      |

| Table 37 | AC Characteristics of the Power Supply                                         |      |

| Table 38 | Timing Characteristics of the MDIO Interface                                   |      |

| Table 39 | Transmit Timing Characteristics of the SGMII                                   |      |

| Table 40 | Receive Timing Characteristics of the SGMII                                    |      |

| Table 41 | SPI Interface Timing Parameters                                                |      |

| Table 42 | JTAG Interface Clock                                                           |      |

| Table 43 | JTAG Timing                                                                    |      |

| Table 44 | Specification of the Crystal                                                   |      |

| Table 45 | Electrical Characteristics for Common-Mode Rejection and Termination Circuitry |      |

| Table 46 | Electrical Characteristics for Supported Transformers (Magnetics)              |      |

| Table 47 | Electrical Characteristics for Supported RJ45 Plugs                            |      |

| Table 48 | Calibration Resistors Values.                                                  |      |

| Table 49 | External Component Values for DC/DC Converter                                  | 181  |

# Ethernet Network Connection GPY211 (GPY211B1VC, GPY211C0VC)

### List of Tables

| Table 50 | JEDEC Thermal Resistance Package Parameter - Still air conditions              | 183 |

|----------|--------------------------------------------------------------------------------|-----|

| Table 51 | JEDEC Thermal Resistance Package Parameter - With Thermal Solution Environment | 183 |

| Table 52 | JEDEC Thermal Resistance Package Parameter - Compact 2-R Model Network         | 183 |

| Table 53 | Chip Marking Pattern                                                           | 185 |

| Table 54 | Product Naming (GPY211C0VC)                                                    | 185 |

| Table 55 | Product Naming (GPY211B1VC)                                                    | 185 |

# 1 **Product Overview**

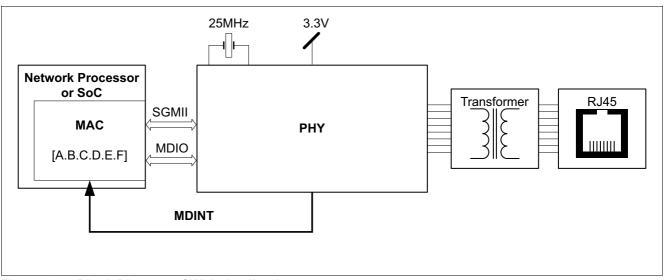

The Ethernet Network Connection GPY211 is a low power Ethernet PHY transceiver integrated circuit. It offers a cost-optimized solution that is well-suited for routers, switches, and home gateways. It performs the data transmission on an Ethernet twisted pair copper cable of category Cat5e or higher. GPY211 supports the following data rates: 2500, 1000, 100, and 10 Mbit/s.

In terms of the Open System Interconnection (OSI) model, the GPY211 implements a layer 1 physical media access device. It can be connected to another chip implementing a layer 2 MAC via a serial SGMII data interface.

On the Ethernet twisted pair interface, the GPY211 is compliant with the following standards from IEEE 802.3 referenced in [2] and [3]: 2.5GBASE-T (IEEE 802.3bz, NBASE-T), 1000BASE-T (IEEE802.3 Clause 40), 100BASE-TX (IEEE 802.3 Clause 25) and 10BASE-Te (IEEE 802.3 Clause 14). This interface supports the Energy-Efficient Ethernet feature to reduce idle mode power consumption. Power saving at the system level is also possible with the Wake-on-LAN feature. A low-EMI line driver with integrated termination facilitates the PCB design.

On the SGMII interface, connecting to another chip implementing a MAC layer, the GPY211 supports the following standards: IEEE802.3 Clause 36 and 27 [2], and Cisco SGMII [4]. This interface also operates at data rates: 2500, 1000, 100, and 10 Mbit/s.

The GPY211 supports the Precision Time Protocol (PTP).

The GPY211 supports a standard MDIO management interface as defined in IEEE 802.3 Clause 22 and Clause 45 [2], [3]. The MDIO serial interface can operate with a clock running up to 25 MHz. It allows a management entity (the external chip implementing the MAC) to access standard MDIO / MMD registers to control the GPY211 behavior, or to read the link status. In addition, two vendor specific register banks (VSPEC1 and VSPEC2) allow GPY211 specific configuration of LED, SGMII, and Wake-on-LAN features. The MDIO and MMD registers are documented in Chapter 5. The GPY211 is also configurable via pin strapping.

The GPY211 can drive up to four LEDs. Each LED is independently programmable to indicate the link speed, and traffic activities. Several indication schemes can be selected.

A DC/DC converter is integrated within the GPY211. A single external power supply of 3.3 V is sufficient to power the chip, with the internal DC/DC converter generating 1.0 V to supply the low voltage domains. External supply of both 3.3 V and 1.0 V is also an option.

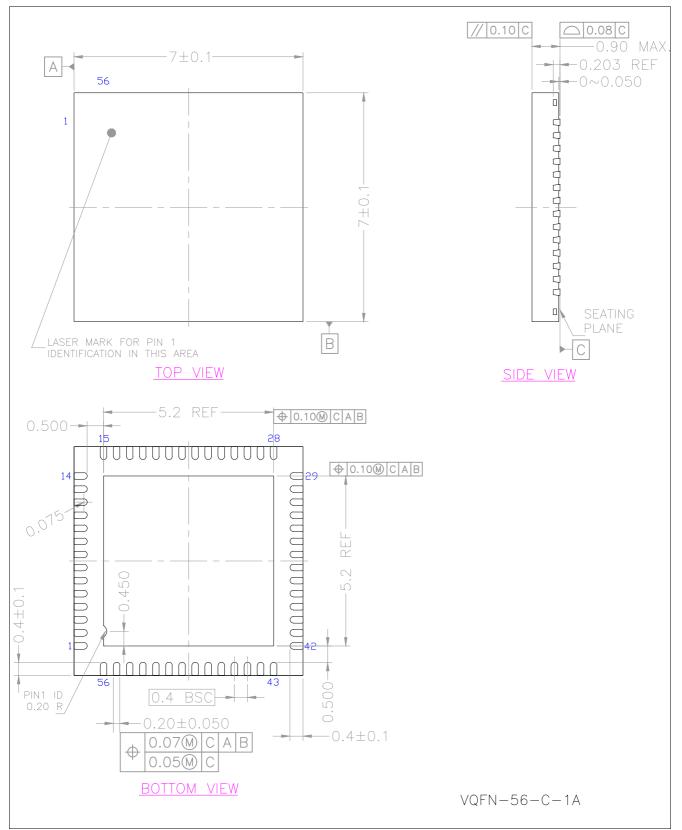

The GPY211 uses a single row package (type PG-VQFN-56, size 7 mm x 7 mm).

## 1.1 Features

This chapter provides an overview of the features supported by the GPY211:

### **Communication Interfaces**

- The multiple speed, single-port Ethernet PHY interface to the twisted pair cable supports:

- Ethernet modes and standards: 2.5GBASE-T (IEEE 802.3bz, NBASE-T), 1000BASE-T (IEEE 802.3), 100BASE-TX (IEEE 802.3) and 10BASE-Te (IEEE 802.3)

- Ethernet twisted pair copper cable of category CAT5 or higher

- Low EMI voltage mode line driver with integrated termination resistors

- Transformerless Ethernet for backplane applications

- Auto-negotiation (ANEG) with extended next page support

- Auto-MDIX and polarity correction

- Auto-downspeed (ADS)

- Energy-Efficient Ethernet (EEE) and power down mode

- Wake-on-LAN (WoL)

- Power-over-Ethernet (POE)

- Precise time stamping, implementing standard IEEE 1588v2

- SPI interface supports Secure Field Firmware Upgrade (FFU) of the flash memory

- The SGMII SerDes interface supports:

- 1000BASE-X IEEE 802.3 Clause 36 and 37 [2]

- Cisco\* Serial-GMII Specification [4] operating at 1.25 Gbaud/s

- Extension of 1000BASE-X and Cisco Serial-GMII to achieve 3.125 Gbaud/s by overclocking the SerDes to support the 2.5 Gbit/s data rate

- Clock and Data Recovery (CDR)

- SGMII power saving when a Low Power Indication (LPI) is active

- The management interface supports the communication between the Station Management (acronym "STA" per IEEE 802.3) and the GPY211 using:

- An MDIO slave interface that provides access to the standard registers in the MMD as described in IEEE 802.3 Clause 22 and Clause 45 [2] and listed in Chapter 5

- An MDIO interface clock of up to 25 MHz

- 3 MDIO message frame types as described in IEEE 802.3: Clause 22, Clause 22 Extended, Clause 45 [2]

- The LED interface supports:

- Up to 4 LEDs

- Single and dual color LEDs

- Connection of LED to ground or 3.3 V

- Several LED indication schemes (link/activity, link speed)

- Configuration of LED indication via MDIO registers

- Control of LED brightness via software driver API

- Alternative configuration of LED pins as GPIO for custom indication

- Supports two external interrupts EXINT0 and EXINT1:

- Configurable as input from, or output to an external controller

### **Clocking, Timing and Time Stamping Features**

- 25 MHz crystal operation

- Supports precise time stamping (PTP) according to standard IEEE 1588v2

- Supports two general purpose clock pins GPC1 and GPC2 shared with GPIO for several usage options, configurable by GPY API:

- to input or output the precise time stamping signals (PTP)

- to output the pulse per second signal (PPS)

#### **Test Features**

- JTAG boundary scan

- · Cable diagnostics: cable open/short detection and cable length estimation

- UART

#### **Power Supply**

- Single 3.3 V power supply, when using the integrated DC/DC converter to generate the 1.0 V power supply rail

- If the internal integrated DC/DC converter is not used, an additional 1.0 V supply must be provided externally

- Ultra low power mode to reduce the energy consumption down to 10 mW when the Ethernet cable is unplugged, with automatic wake-up upon energy detection from cable

## 1.2 Block Diagram

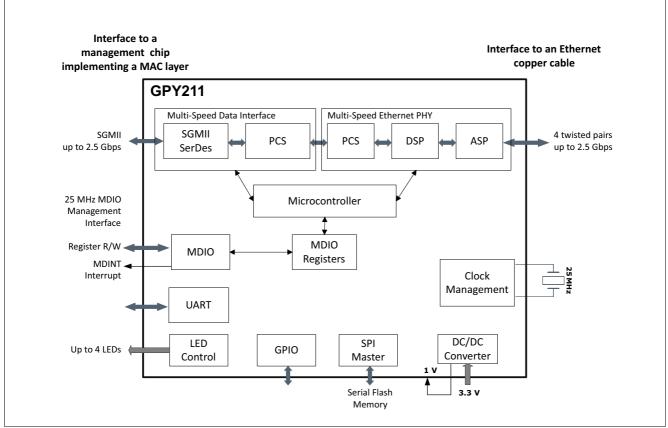

Figure 2 shows the block diagram of the GPY211. The main interfaces are:

- · Data interface to a MAC processor, using SGMII

- Slave control interface driven by a MAC processor, using MDIO slave

- Interrupt signal MDINT allowing the GPY211 to notify the MAC processor about a change of status

- LED control

- Twisted pair interface

Figure 1 Ethernet Network Connection GPY211 Block Diagram

# 2 External Signals

This chapter describes the signal mapping to the package.

# 2.1 Overview

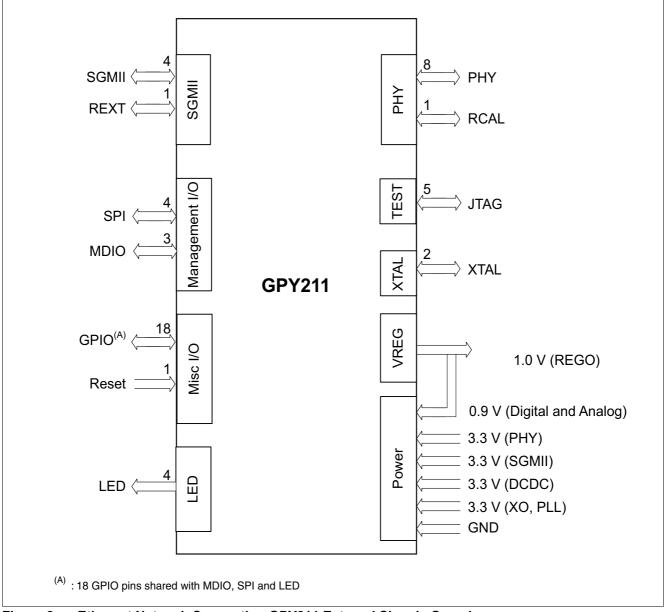

Figure 2 provides an overview of the external interfaces of the GPY211.

Figure 2 Ethernet Network Connection GPY211 External Signals Overview

# 2.2 External Signal Description

This chapter provides the pin diagram, abbreviations for pin types and buffer types, as well as tables describing the input and output signals.

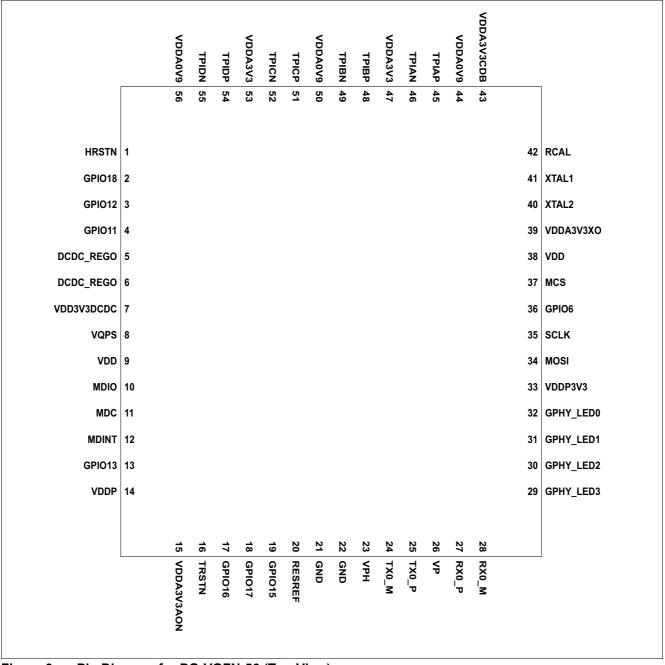

## 2.2.1 Pin Diagram

The pin layout of the package is shown in Figure 3.

Figure 3 Pin Diagram for PG-VQFN-56 (Top View)

# 2.2.2 Abbreviations

Abbreviations that are used in the signal tables are summarized in Table 1 and Table 2.

### Table 1 Abbreviations for Pin Type

| Abbreviations                | Description                                                                          |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| I Input only, digital levels |                                                                                      |  |  |  |

| 0                            | Output only, digital levels                                                          |  |  |  |

| I/O                          | Bidirectional input/output signal, digital levels                                    |  |  |  |

| Prg                          | Bidirectional pad, programmable to operate either as input or output, digital levels |  |  |  |

| AI                           | Input only, analog levels                                                            |  |  |  |

| AO                           | Output only, analog levels                                                           |  |  |  |

| AI/O                         | Bidirectional, analog levels                                                         |  |  |  |

| PWR                          | Power                                                                                |  |  |  |

| GND                          | Ground                                                                               |  |  |  |

### Table 2Abbreviations for Buffer Type

| Abbreviations | Description                                                         |

|---------------|---------------------------------------------------------------------|

| A             | Analog characteristics, see the AC/DC specification for more detail |

| GND           | Ground                                                              |

| Prg           | Programmable with an alternate function                             |

# 2.2.3 Input/Output Signals

A detailed description of all the pins is given in **Table 3** to **Table 8**.

In **Table 5** to **Table 8**, the signal names highlighted in bold are the same as the pin name. The signal names that are not in bold indicate alternate functions.

# 2.2.3.1 Ethernet Media Interface

| Table 5  |                 |                |                |                                                                       |  |

|----------|-----------------|----------------|----------------|-----------------------------------------------------------------------|--|

| Pin No.  | Name            | Pin<br>Type    | Buffer<br>Type | Function                                                              |  |

| Ethernet | Port Ethernet   | Media Interfac | e              |                                                                       |  |

| 45       | ΤΡΙΑΡ           | AI/AO          | А              | Twisted Pair Transmit/Receive Positive/Negative                       |  |

| 46       | TPIAN           | AI/AO          | А              | _                                                                     |  |

| 48       | TPIBP           | AI/AO          | А              |                                                                       |  |

| 49       | TPIBN           | AI/AO          | А              |                                                                       |  |

| 51       | TPICP           | AI/AO          | А              |                                                                       |  |

| 52       | TPICN           | AI/AO          | А              |                                                                       |  |

| 54       | TPIDP           | AI/AO          | А              |                                                                       |  |

| 55       | TPIDN           | AI/AO          | А              |                                                                       |  |

| Ethernet | Port Calibratio | n              | -              |                                                                       |  |

| 42       | RCAL            | AI/AO          | A              | Calibration of GPHY Ethernet Port<br>Using a high precision resistor. |  |

|          |                 |                |                |                                                                       |  |

### Table 3 Ethernet Media Interface Signals

# 2.2.3.2 SGMII Interface

| Table 4 | SGMII | Interface | Signals |

|---------|-------|-----------|---------|

|---------|-------|-----------|---------|

| Pin No. | Name   | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                  |

|---------|--------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28      | RX0_M  | AI          | А              | Differential SGMII Data Input Pair                                                                                                                                                                                                                                        |

| 27      | RX0_P  | AI          | A              | These are the negative and positive signals respectively of<br>the differential input pair of the SGMII SerDes interface. Due<br>to the integrated CDR, no external transmission of source-<br>synchronous clock is required for SGMII. These pins must be<br>AC coupled. |

| 25      | TX0_P  | AO          | A              | Differential SGMII Data Output Pair                                                                                                                                                                                                                                       |

| 24      | ТХ0_М  | AO          | A              | These are the negative and positive signals respectively of the differential output pair of the SGMII SerDes interface.                                                                                                                                                   |

| 20      | RESREF | AI/O        | А              | Pad to Connect External Tuning Resistor                                                                                                                                                                                                                                   |

| 21      | GND    | AI          | GND            | Connect to Ground                                                                                                                                                                                                                                                         |

| 22      | GND    | AI          | GND            | Connect to Ground                                                                                                                                                                                                                                                         |

# 2.2.3.3 LED/JTAG/GPIO Interface

The LED interface allows external LEDs to be connected to indicate the status of the Ethernet PHY interfaces. Single and dual color LEDs are supported.

| Pin No.  | Name      | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                              |

|----------|-----------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED Sigr | nals      |             | -1             |                                                                                                                                                                       |

| 32       | GPHY_LED0 | 0           |                | <b>GPHY LED0</b><br>LED control output, freely configurable, drives single color or dua color LEDs.                                                                   |

| 31       | GPHY_LED1 | 0           |                | <b>GPHY LED1</b><br>LED control output, freely configurable, drives single color or dua color LEDs.                                                                   |

| 30       | GPHY_LED2 | 0           |                | <b>GPHY LED2</b><br>LED control output, freely configurable, drives single color or dua color LEDs.                                                                   |

| 29       | GPHY_LED3 | I/O         | Prg            | <b>GPHY LED3</b><br>LED control output, freely configurable, drives single color or dua color LEDs.<br>This pin is also used for the brightness control switch input. |

|          | ТСК       | I           | PU             | <b>JTAG Test Clock</b><br>The signals TDI, TDO and TMS are synchronous subject to this<br>JTAG test clock.                                                            |

| 16       | TRSTN     | I           | PD             | <b>JTAG Test Reset</b><br>The signal TRSTN must be pulled-down to ground. The JTAG is<br>only used in production for boundary scan.                                   |

| 19       | GPIO15    | Prg         | Prg            | <b>General Purpose IO 15</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                       |

|          | TDI       | I           | PU             | JTAG Serial Test Data Input                                                                                                                                           |

| 17       | GPIO16    | Prg         | Prg            | <b>General Purpose IO 16</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                       |

|          | TMS       | I           | PU             | JTAG Test Mode Select                                                                                                                                                 |

| 18       | GPIO17    | Prg         | Prg            | <b>General Purpose IO 17</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                       |

|          | TDO       | 0           |                | JTAG Serial Test Data Output<br>JTAG test data output.                                                                                                                |

# 2.2.3.4 Management Interfaces

Two types of serial management interface are provided:

- SPI master interface

- MDIO slave interface

### Table 6 Management Interface Signals

| Pin No.  | Name          | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                        |

|----------|---------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIO SIa | ave Interface | ,           |                |                                                                                                                                                                                                                 |

| 4        | GPIO11        | Prg         | Prg            | <b>General Purpose IO 11</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                                                                 |

|          | GPC1          | Prg         |                | General Purpose Clock 1<br>General purpose clock. Either input or output mode can be<br>selected.                                                                                                               |

| 11       | MDC           | 1           | Prg            | MDIO Slave Clock<br>The external controller host (also called "STA" in IEEE standard)<br>acts as clock master and provides the serial clock of up to 25 MHz<br>on this input.                                   |

| 10       | MDIO          | I/O         | Prg            | MDIO Slave Data Input/Output<br>The external controller host (also called "STA" in IEEE standard)<br>uses this signal to address internal registers and to transfer data<br>to and from the internal registers. |

| SPI Mast | er Interface  |             |                |                                                                                                                                                                                                                 |

| 36       | GPIO6         | Prg         | Prg            | <b>General Purpose IO 6</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                                                                  |

|          | MISO          | I           |                | SPI Data Input<br>SPI interface data input.                                                                                                                                                                     |

| 34       | MOSI          | 0           | Prg            | SPI Data Output<br>SPI interface data output.                                                                                                                                                                   |

SCLK

MCS

35

37

0

0

Prg

Prg

**SPI Clock**

SPI interface clock.

SPI interface chip select. Active low signal.

**SPI Chip Select**

#### **Miscellaneous Signals** 2.2.3.5

| Table 7  | Miscellane | ous Signal  | s              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.  | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Reset an | d Clocking |             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 41       | XTAL1      | AI          | A              | <b>Crystal: Oscillator Input</b><br>A crystal must be connected between XTAL1 and XTAL2.<br>Additional load capacitances must also tie both pins to GND.                                                                                                                                                                                                                                                                                                                                                                     |

|          | CLK        | I           |                | <b>Clock: Clock Input</b><br>The clock must have a frequency accuracy of ±50 ppm.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40       | XTAL2      | AO          | A              | <b>Crystal: Oscillator Output</b><br>A crystal must be connected between XTAL1 and XTAL2.<br>Additional load capacitances must also tie both pins to GND.                                                                                                                                                                                                                                                                                                                                                                    |

| 13       | GPIO13     | Prg         | Prg            | <b>General Purpose IO 13</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                                                                                                                                                                                                                                                                                                                                                                              |

|          | EXINT0     |             |                | <b>External Interrupt 0</b><br>This is an interrupt signal to or from an external host.<br>Configurable as input or output.<br>This is not used in the standard application.                                                                                                                                                                                                                                                                                                                                                 |

| 12       | GPIO14     | Prg         | Prg            | General Purpose IO 14<br>Configurable as input or output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | EXINT1     |             |                | <b>External Interrupt 1</b><br>This is an interrupt signal to or from an external host.<br>Configurable as input or output.<br>This is not used in the standard application.                                                                                                                                                                                                                                                                                                                                                 |

|          | MDINT      | 0           |                | MDIO Interrupt<br>The MDINT signal is used to send an interrupt to an external MAC<br>SoC acting as station manager (STA). The STA can program its<br>sensitivity to specific events using the PHY_IMASK register. The<br>MDINT event is then raised when the event occurs using the<br>polarity programmed by pin strap. The STA can read which type<br>of event occurred in the PHY_ISTAT register. Upon read of<br>PHY_ISTAT by the STA, the MDINT is deasserted by the<br>GPY211. Refer to Figure 9 for further details. |

| 3        | GPIO12     | Prg         | Prg            | General Purpose IO 12<br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                                                                                                                                                                                                                                                                                                                                                                                     |

|          | GPC2       | Prg         |                | <b>General Purpose Clock 2</b><br>General purpose clock. Either input or output mode can be selected.                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Tabla 7 ... ... ~ . .

| Pin No. | Name   | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                 |

|---------|--------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | GPIO18 | Prg         | Prg            | <b>General Purpose IO 18</b><br>Configurable as input or output.<br>The output characteristic can be selected to be open drain or<br>push-pull.                                          |

| 1       | HRSTN  | 1           | PU             | Hardware Reset<br>Asynchronous active low device reset. If the internal Power-on-<br>Reset (POR) circuit is used to trigger the device power up, this<br>signal can be left unconnected. |

# Table 7Miscellaneous Signals (cont'd)

## 2.2.3.6 Power Supply

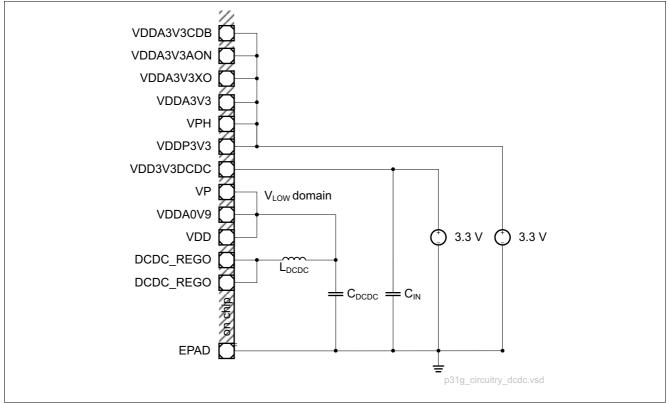

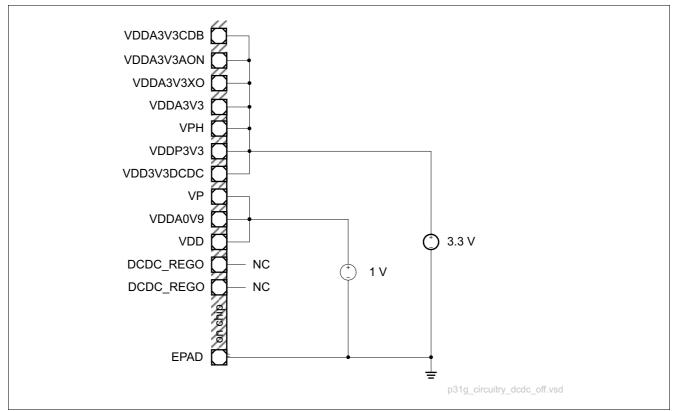

This section specifies the power supply pins. They are categorized in 2 supply groups  $V_{HIGH}$  (3.3 V) and  $V_{LOW}$  (1.0 V). The  $V_{LOW}$  domain can either be supplied externally, or self-generated by the internal DC/DC SVR converter, which converts the VDD3V3DCDC 3.3 V supply into DCDC\_REGO output. In the external supply configuration, the DCDC\_REGO output pins are non connected (NC). In the internal DC/DC SVR converter configuration, the DCDC\_REGO output pins are connected back to the V<sub>LOW</sub> supply inputs.

| Pin No.       | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47, 53        | VDDA3V3    | PWR         |                | <b>High Voltage Domain Supply V</b> <sub>HIGH</sub><br>These are the input power pins for the analog front end in the high voltage domain. They have to be supplied with a nominal voltage of $V_{DDA3V3}$ = 3.3 V.                                                                                                                                                                                                                                                    |

| 44, 50,<br>56 | VDDA0V9    | PWR         |                | <b>Low Voltage Domain Supply V</b> <sub>LOW</sub><br>These are the input power supply pins for the low voltage domain.<br>They supply mixed signal blocks in the analog front end and the<br>clock distribution block of the Gigabit Ethernet PHY. These pins<br>have to be supplied with a nominal voltage of $V_{DDA0V9} = 1.0 \text{ V}$ . When<br>the internal DC/DC SVR converter is used, they have to be<br>connected to the output of the converter DCDC_REGO. |

| 39            | VDDA3V3XO  | PWR         |                | <b>XO Pad Voltage Domain Supply V<sub>HIGH</sub></b><br>This is the input power supply pin for the internal PLL and the internal crystal oscillator (XO). This pin has to be supplied with a nominal voltage of $V_{DDA3V3}$ = 3.3 V.                                                                                                                                                                                                                                  |

| 43            | VDDA3V3CDB | PWR         |                | <b>CDB High Voltage Domain Supply V</b> <sub>HIGH</sub><br>This is the input power supply pin for the internal clock distribution<br>block (CDB). This pin has to be supplied with a nominal voltage of<br>$V_{DDA3V3}$ = 3.3 V.                                                                                                                                                                                                                                       |

| 15            | VDDA3V3AON | PWR         |                | AON High Voltage Domain Supply $V_{HIGH}$<br>This is the input power supply pin for the Always On Domain (AON).<br>This pin has to be supplied with a nominal voltage of $V_{DDA3V3}$ = 3.3 V.                                                                                                                                                                                                                                                                         |

# Table 8 Power Supply Pins

| Pin No. | Name       | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26      | VP         | PWR         |                | <b>SGMII Low Voltage Domain Supply V</b> <sub>LOW</sub><br>This is the pin for the low voltage domain of the SGMII interface. If<br>supplies mixed signal blocks in the SGMII interface. This pin has to<br>be supplied with a nominal voltage of $V_P = 1.0$ V. When the interna<br>DC/DC SVR converter is used, these pins have to be connected to<br>the output of the converter DCDC_REGO.                                                                                                                                                                                                                          |

| 23      | VPH        | PWR         |                | <b>SGMII High Voltage Domain Supply V<sub>HIGH</sub></b><br>This is the pin for the high voltage domain of the SGMII interface. If<br>supplies mixed signal blocks in the PHY of the SGMII interface.<br>This pin has to be supplied with a nominal voltage of $V_{PH}$ = 3.3 V.                                                                                                                                                                                                                                                                                                                                        |

|         | VDDP       | PWR         |                | <b>Configurable MDIO Pad Voltage Domain Supply</b><br>This is the group of supply pins for the MDIO pins group (pin 10 to 13).<br>This group can be configured in 1.8 V or 3.3 V operation, depending on the option selected by pin strap on pin 19 (PS_MDIO_VOLTAGE).<br>When PS_MDIO_VOLTAGE is LOW, this pin has to be supplied with a nominal voltage of $V_{DDP}$ = 1.8 V.<br>When PS_MDIO_VOLTAGE is HIGH, this pin has to be supplied with a nominal voltage of $V_{DDP}$ = 3.3 V. An internal Pull up on pin 19 drives the pin 19 configuration to HIGH unless the pin is explicitly connected to ground (LOW). |

| 33      | VDDP3V3    | PWR         |                | <b>Pad Voltage Domain Supply V<sub>HIGH</sub></b><br>This is the group of supply pins for the pad supply of GPIO pins<br>(except the MDIO group of pin which is supplied by VDDP)<br>This pin has to be supplied with a nominal voltage of<br>$V_{DDP3V3} = 3.3 V.$                                                                                                                                                                                                                                                                                                                                                     |

| 9, 38   | VDD        | PWR         |                | <b>Core Voltage Domain Supply V</b> <sub>LOW</sub><br>This is the group of supply pins for the core digital voltage domain.<br>This pin has to be supplied with a nominal voltage of $V_{DD}$ = 1.0 V.<br>When the internal DC/DC SVR converter is used, these pins have<br>to be connected to the output of the converter DCDC_REGO.                                                                                                                                                                                                                                                                                   |

| 8       | VQPS       | PWR         |                | <b>Ground</b><br>This pin is not used in application mode. It must be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7       | VDD3V3DCDC | PWR         |                | <b>Internal DC/DC SVR Converter Power Supply V<sub>HIGH</sub></b><br>This is the supply pin for the integrated DC/DC converter. This pin<br>has to be supplied with a nominal voltage of V <sub>DDA3V3DCDC</sub> = 3.3 V.<br>This pin must be connected in all supply configuration including the<br>external V <sub>LOW</sub> supply option.                                                                                                                                                                                                                                                                           |

| 5, 6    | DCDC_REGO  | PWR         |                | <b>Internal DC/DC SVR Converter Output</b><br>These are the 2 pins supplying the V <sub>LOW</sub> domain when the internal DC/DC SVR converter is used. In internal SVR mode this pin must be connected back to the V <sub>LOW</sub> domain to self supply the chip. The connection circuitry for the internal DCDC SVR V <sub>LOW</sub> supply option and the external V <sub>LOW</sub> supply option are described in Figure 28 and Figure 29.                                                                                                                                                                        |

### Table 8 Power Supply Pins

### Table 9Device Ground

| Pin No.            | Name | Pin Type | Buffer Type | Function       |

|--------------------|------|----------|-------------|----------------|

| EPAD <sup>1)</sup> | VSS  | GND      |             | General Device |

|                    |      |          |             | Ground         |

1) The EPAD is the exposed pad on the bottom of the package. This pad must be properly connected to the ground plane of the PCB.

# 3 Functional Description

# 3.1 Power Supply, Clock and Reset

This chapter provides the information required to power up the GPY211.

## 3.1.1 Power Supply

Two power supply options are available:

- A single external power supply of 3.3 V with this option the internal DC/DC SVR converter generates the required 1.0 V supply.

- Two external power supplies of 3.3 V and 1.0 V with this option, the internal DC/DC SVR converter is not used.

The detailed power supply connection requirements are documented in **Chapter 7.7**. The differentiation between the two power supply options is done by connecting, or not the pins DCDC\_REGO as details in **Figure 28** and **Figure 29**.

# 3.1.2 Clock Generation

An external 25 MHz crystal must be connected to the GPY211. The required crystal specification is documented in **Chapter 7.5.8**. An internal PLL circuit generates all the required internal clocks.

## 3.1.3 Reset Generation

The external hardware reset input (HRSTN pin) resets all the hardware modules, except the DC/DC converter:

- Driving the HRSTN pin low causes an asynchronous reset of the GPY211 system.

- Releasing the HRSTN pin high triggers the power-on sequence and boot-up procedure.

The HRSTN pin is internally connected to a weak internal pull-up resistor.

## 3.1.4 Power-On Sequence

The GPY211 powers on when the power is applied as shown in **Figure 19**. The following steps are executed at power on:

- Locking of internal PLL.

- Calibration of internal voltage using a high precision external reference resistor connected to the RCAL pin.

- Reading of pin strap information, as described in Chapter 3.1.5.

- Booting of the microprocessor from internal ROM.

- Auto-negotiation on the Ethernet twisted pair interface and SGMII interface using the speed capability of 2.5 Gbit/s, full-duplex.

- Training and link up in accordance with the IEEE 802.3 [2] and SGMII [4] standards.

# 3.1.5 Configuration by Pin Strapping

The GPY211 device can be configured by means of pin strapping on a number of the GPIO pins. The pin strapping configurations are captured during the chip power-on sequence, until the reset initialization is complete.

The pin strap values can be set to logical high or low by connecting the corresponding pin via an external 1 k $\Omega$  resistor to either ground or 3.3 V.

The pin strap mapping is described in **Table 10** and **Table 11**.

| Pin Name | Pin Number | <b>Configuration Item Description</b> |  |  |  |  |

|----------|------------|---------------------------------------|--|--|--|--|

| MCS      | 37         | PS_PHY_MADDR(0)                       |  |  |  |  |

| SCLK 35  |            | PS_PHY_MADDR(1)                       |  |  |  |  |

| MOSI     | 34         | PS_PHY_MADDR(2)                       |  |  |  |  |

| GPIO12   | 3          | PS_PHY_MADDR(3)                       |  |  |  |  |

| GPIO18   | 2          | PS_PHY_MADDR(4)                       |  |  |  |  |

| MDINT    | 12         | PS_MINT_POL                           |  |  |  |  |

| GPIO17   | 18         | PS_RJ45_TAP                           |  |  |  |  |

| GPIO15   | 19         | PS_MDIO_VOLTAGE                       |  |  |  |  |

### Table 10 Pin Names used for Pin Strapping

| Table 11 | Pin Strapping Configuration Description |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

| Pin Strapping Signals | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS_PHY_MADDR(4:0)     | MDIO PHY Address<br>A high level means a logical 1 and low level means a logical 0.                                                                                                                                                                                                                                                                                                                                                                                                       |